トランジスタ技術 2019年5月号の表記回路に興味を引かれた。黒田徹氏による「ひずみ率0.0005%! 40W高効率パワー・アンプの製作」という記事[1]である。

回路図にちょっと不思議なところもあったので、自分なりに腑に落ちるようLTspiceでいろいろ試してみる。

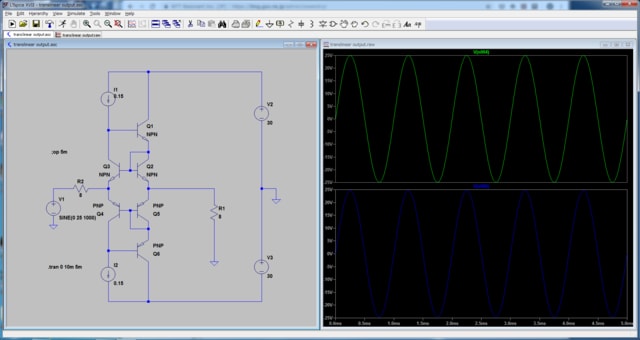

これは、「図5 初代アンプの出力段を簡略化した回路」をLTspiceに入力し、ドライブ波形と出力波形をグラフに出したもの。ドライブアンプは省略。ちゃんと、増幅率1の出力段として動いている。なお、雑誌記事では、間違って図7 と同じタイトルになっている。

次にこれを電流で見てみる。出力電流 I(R1)とドライブ電流 I(R2) はこうなる。60mA p-pで6A p-p に100倍の電流増幅がされている。あるいは、8Ω負荷がドライブ段からは800Ω負荷に軽くなっているということだろう。

[1]: 黒田 徹、「ひずみ率0.0005%! 40W高効率パワー・アンプの製作」、トランジスタ技術 2019年5月号、p179-189.