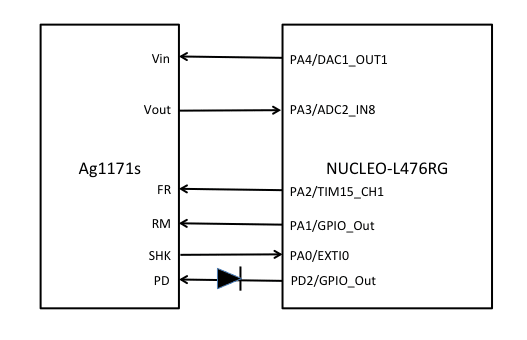

これまでAg1171のPD端子はオープンで使っていましたが、オンフック時の消費電流を削減するためにSTM32につなげてやりました。

PD端子をLレベルにすることでパワーダウンすることができますが、この端子は

オンフックを検出したならば、PD信号をLレベルにすることでAg1171はパワーダウン状態に入ります。しかし、パワーダウン状態ではオフフックの検出ができません。そこで時折パワーダウンを解除して、フッキング状態が変化していないか確認してやる必要があります。しかも、パワーダウンを解除してから信号の状態が安定するまでには50msを要します。オフフックされたことを速やかに検出するためには、頻繁にパワーダウン状態から抜け出さねばならなくなります。

今回はパワーダウン期間を350msにしてみました。その後50msのウエイトを置くのので、オンフック時には400ms間隔で状態確認を行うことになります。実際に試してみると受話器を耳に当てて、ちょっとしてからダイアルトーンが聞こえる感じですが、まぁいいことにしよう。

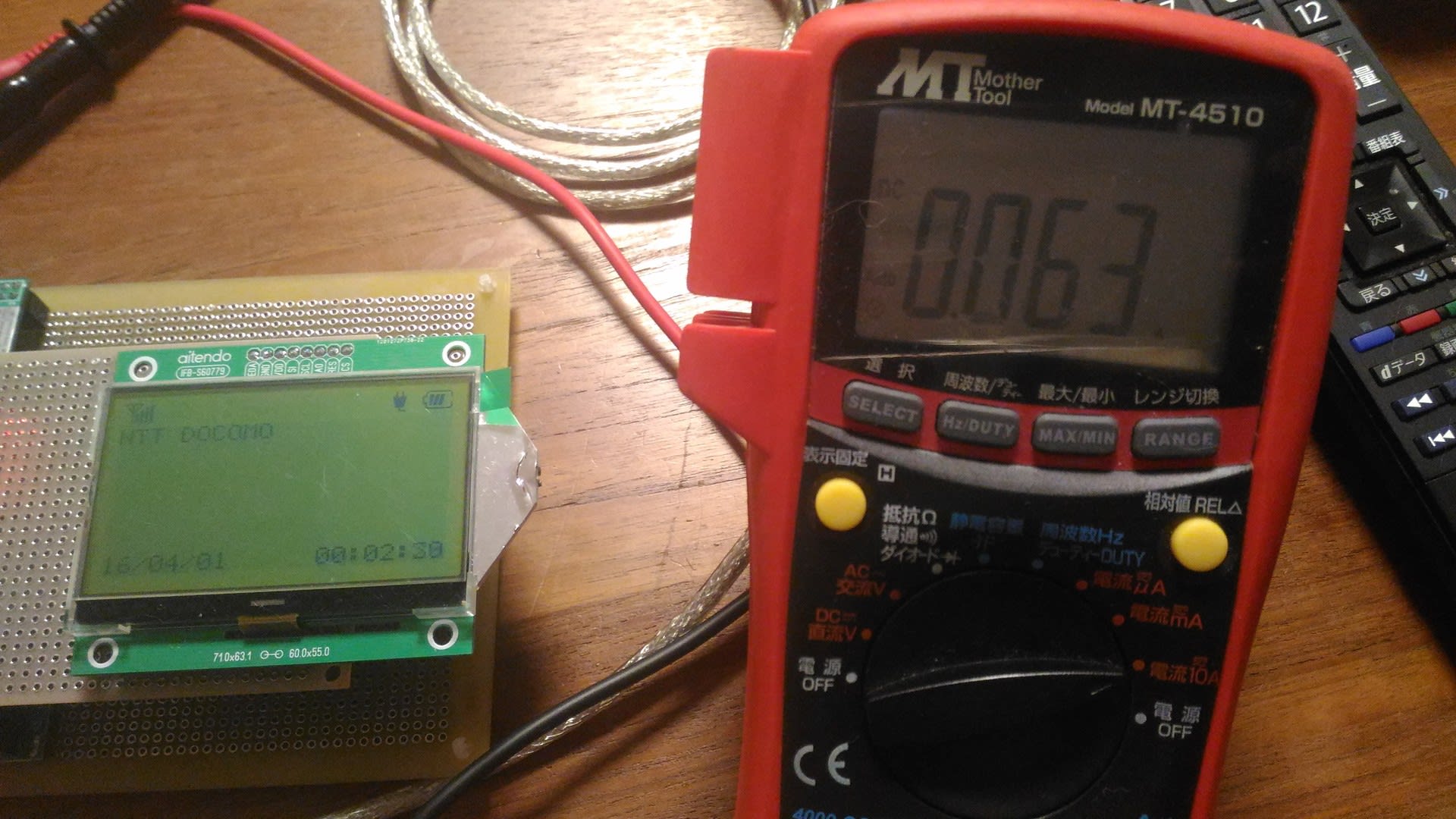

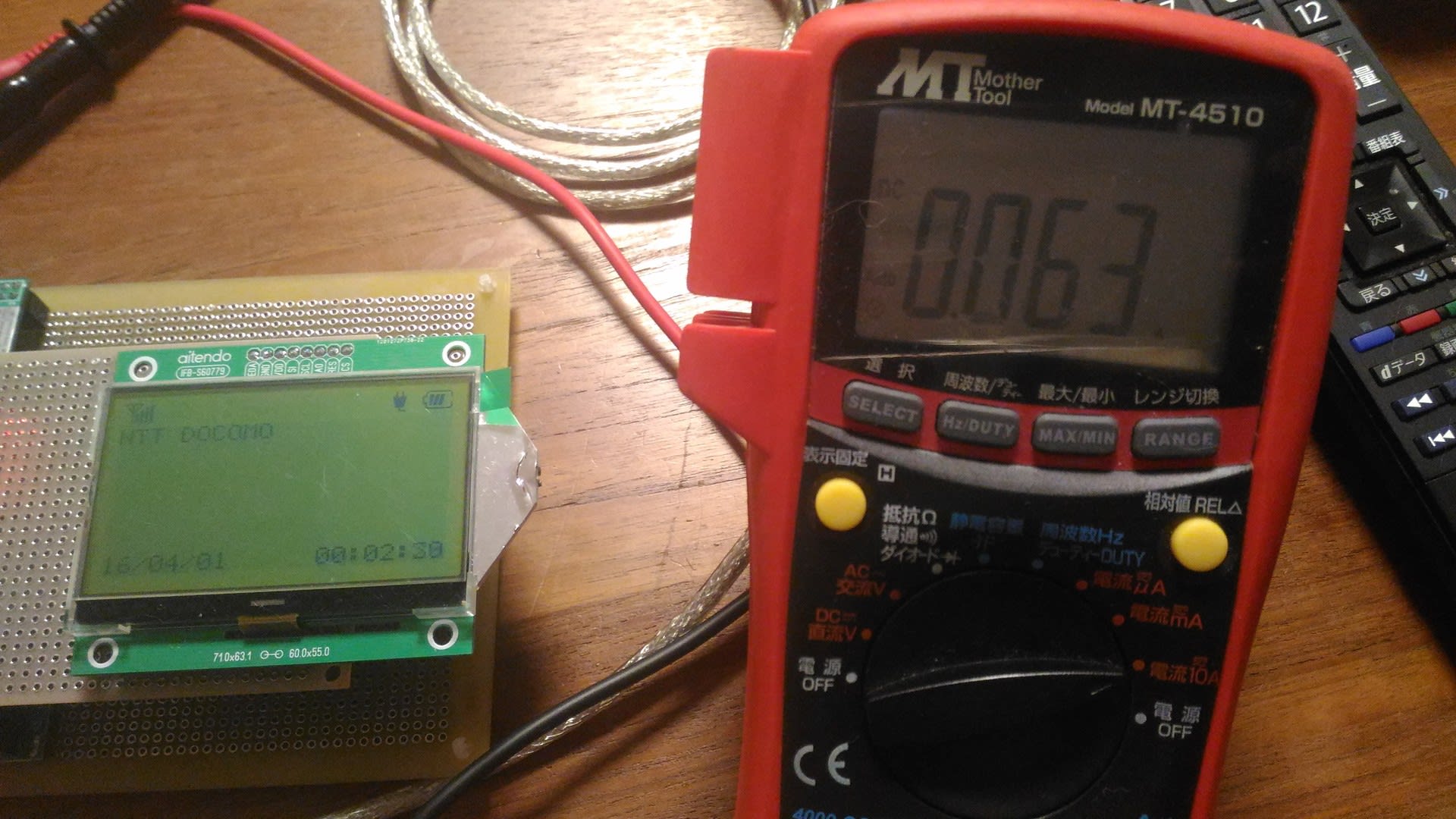

電流を測ってみると、当然のことながら数値が変化します。テスターでは少ない時で63mA程度。70mAほど減ったようです。

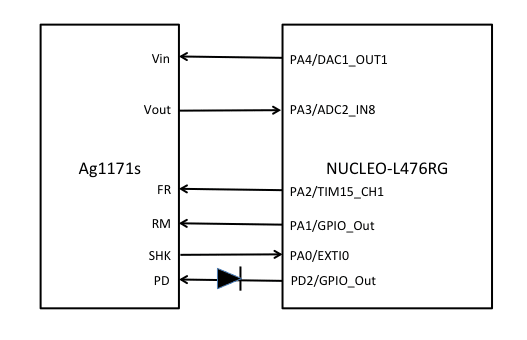

PD端子をLレベルにすることでパワーダウンすることができますが、この端子は

Hレベルにしてはならないことになっているので、上図のようにダイオードを入れて使います。

オンフックを検出したならば、PD信号をLレベルにすることでAg1171はパワーダウン状態に入ります。しかし、パワーダウン状態ではオフフックの検出ができません。そこで時折パワーダウンを解除して、フッキング状態が変化していないか確認してやる必要があります。しかも、パワーダウンを解除してから信号の状態が安定するまでには50msを要します。オフフックされたことを速やかに検出するためには、頻繁にパワーダウン状態から抜け出さねばならなくなります。

今回はパワーダウン期間を350msにしてみました。その後50msのウエイトを置くのので、オンフック時には400ms間隔で状態確認を行うことになります。実際に試してみると受話器を耳に当てて、ちょっとしてからダイアルトーンが聞こえる感じですが、まぁいいことにしよう。

電流を測ってみると、当然のことながら数値が変化します。テスターでは少ない時で63mA程度。70mAほど減ったようです。