これは、ゲート‐ドレイン間の容量Cgdや、位相補償のための容量Ccの効果が、ゲインを+20dB/Decフラットアウトする一方、LeftHalfPlaneのポールと同じように、位相をmax90°進めるからだ。

これを抑えるには、容量に直列に出力からユニティーゲインバッファとうでフィードバック掛けるか、抵抗をつければいい。副作用のポールの増加を考慮し、抵抗を使う場合、この抵抗をNulling Resistorと呼んでいる。

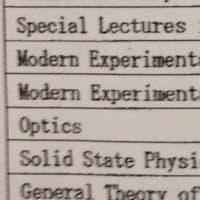

「CMOS Analog Circuit Design Pillip E.Allen & Douglas R.Holberg著」や、

「CMOS JakeBaker著」でも説明されているが、その導出は暗算では無理・・・

ということで、計算してみた。

確かに、Rzが1/gm以上になると、位相が戻る条件ができている。

はじめにやった人は、どうやってこの効果を確かめたのだろう?

数式的にはすごい・・・

ディスクリートのアンプをいじってたら、発振が止まったので、それを物理学者か数学者にでもどういうことか解析してもらったのだろうか?

それとも、直感的に予言できるのだろうか?

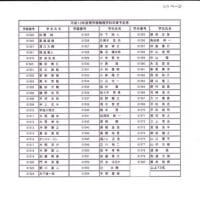

よく見えないでしょうか? フレッシュマンは自分で計算して確認しましょう。

最後にひとつ確認。位相といっても、例えば正弦波は時間と共に変動し、入力も出力もそれぞれに変位に対応する位相があり、こちらは時間の関数である。上記に考察した位相は、スタティックなもので、相対的にどれだけ進んでいるか/遅れているかを表現しているものである。例えば周波数1MHzの入力よりも、45°位相が遅れて出力された信号は、時間的には、入力よりも、1usec*45/360=1/8 usec遅れて振動しているのである。

これを抑えるには、容量に直列に出力からユニティーゲインバッファとうでフィードバック掛けるか、抵抗をつければいい。副作用のポールの増加を考慮し、抵抗を使う場合、この抵抗をNulling Resistorと呼んでいる。

「CMOS Analog Circuit Design Pillip E.Allen & Douglas R.Holberg著」や、

「CMOS JakeBaker著」でも説明されているが、その導出は暗算では無理・・・

ということで、計算してみた。

確かに、Rzが1/gm以上になると、位相が戻る条件ができている。

はじめにやった人は、どうやってこの効果を確かめたのだろう?

数式的にはすごい・・・

ディスクリートのアンプをいじってたら、発振が止まったので、それを物理学者か数学者にでもどういうことか解析してもらったのだろうか?

それとも、直感的に予言できるのだろうか?

よく見えないでしょうか? フレッシュマンは自分で計算して確認しましょう。

最後にひとつ確認。位相といっても、例えば正弦波は時間と共に変動し、入力も出力もそれぞれに変位に対応する位相があり、こちらは時間の関数である。上記に考察した位相は、スタティックなもので、相対的にどれだけ進んでいるか/遅れているかを表現しているものである。例えば周波数1MHzの入力よりも、45°位相が遅れて出力された信号は、時間的には、入力よりも、1usec*45/360=1/8 usec遅れて振動しているのである。