OV2640の出力する信号を確認するために、SaleaeのLogic 8を接続。8chなので、VSYNC, HREF, PCLKに加えてD7..D3の5ビット分のデータをキャプチャしてみました。

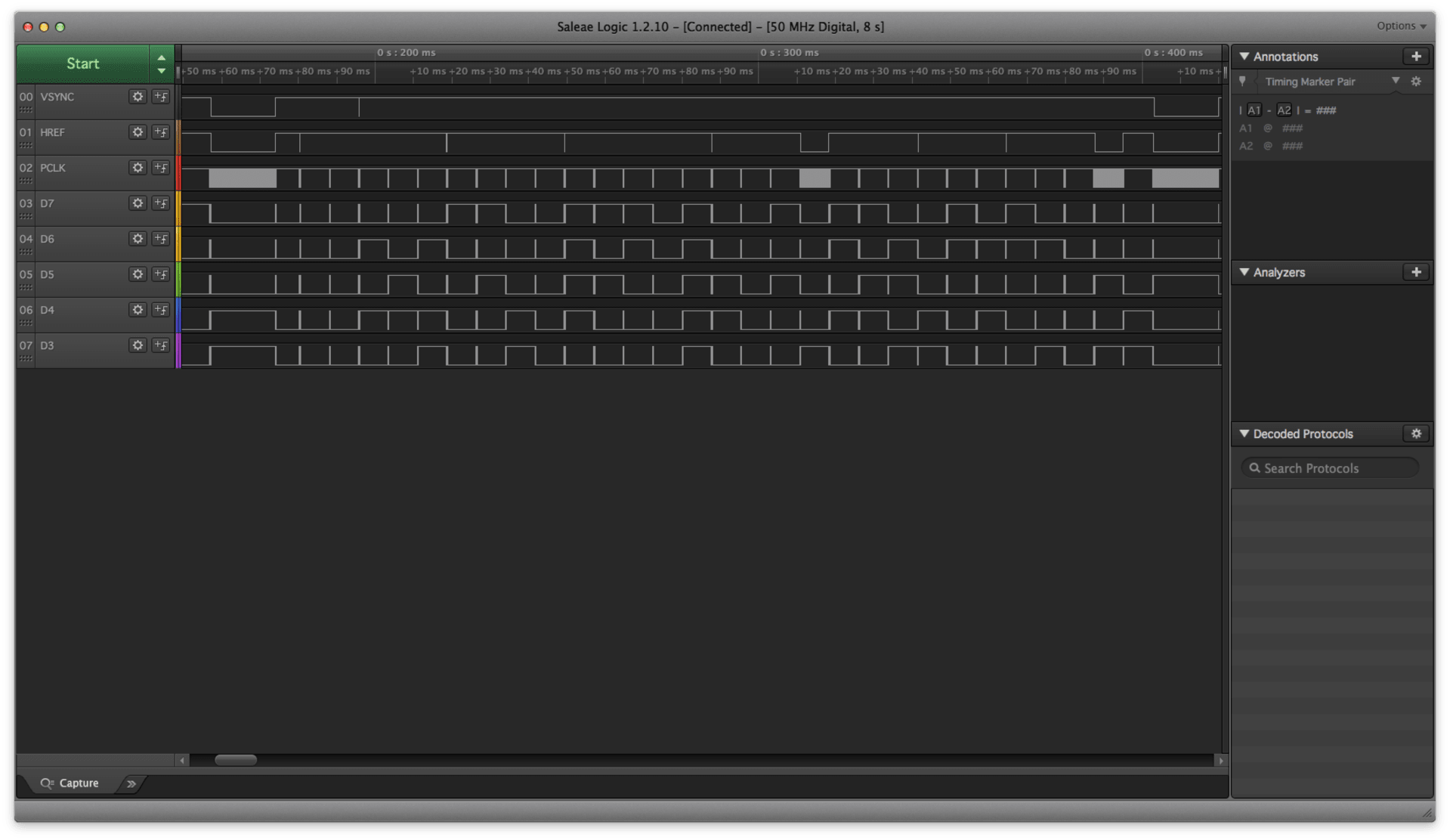

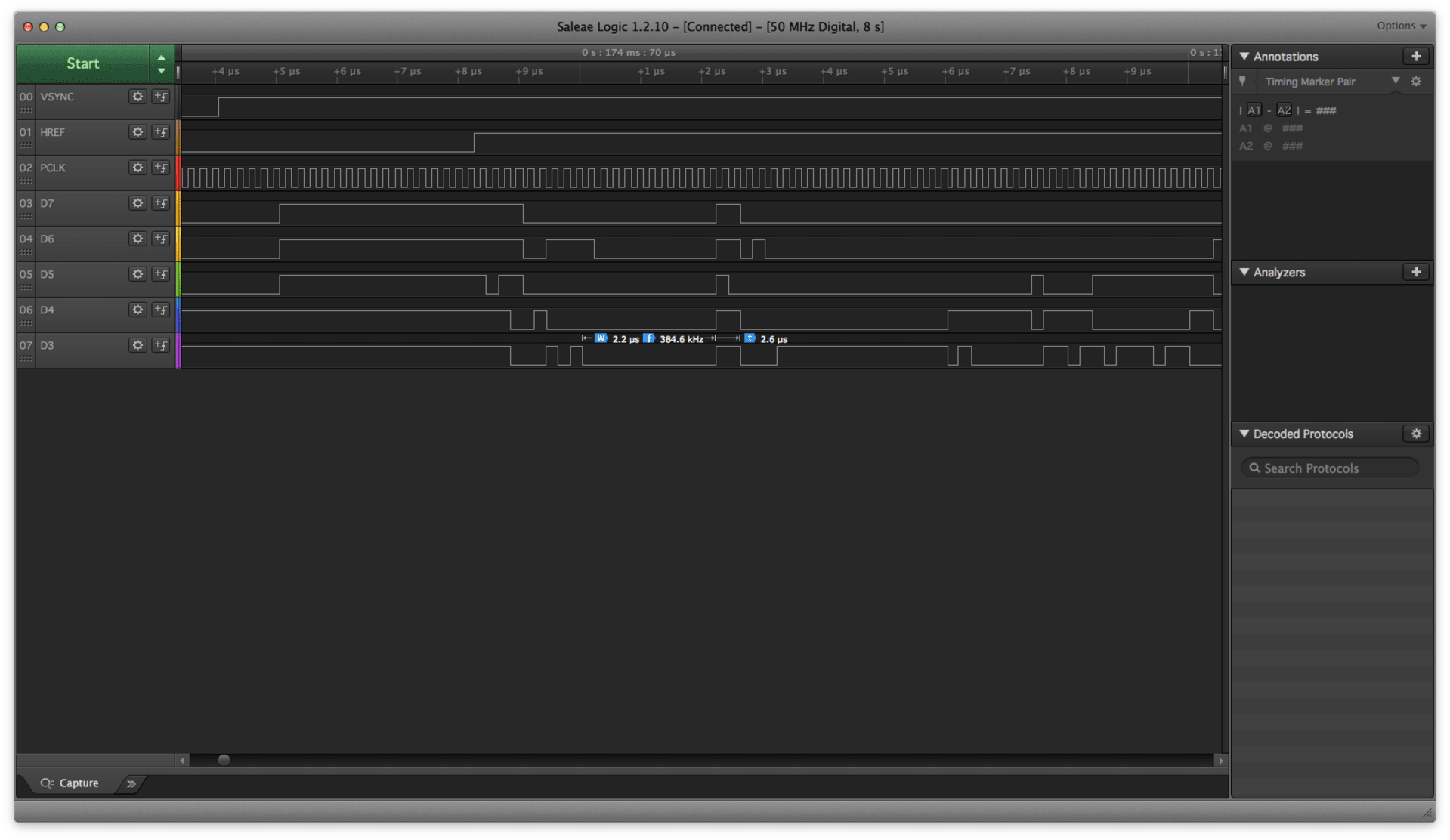

まずはJPEGモードではない、通常形式での出力の場合。

ひとつのVSYNC区間の間に、HREFがライン数回変化していることがわかります。PCLKは出っぱなし。

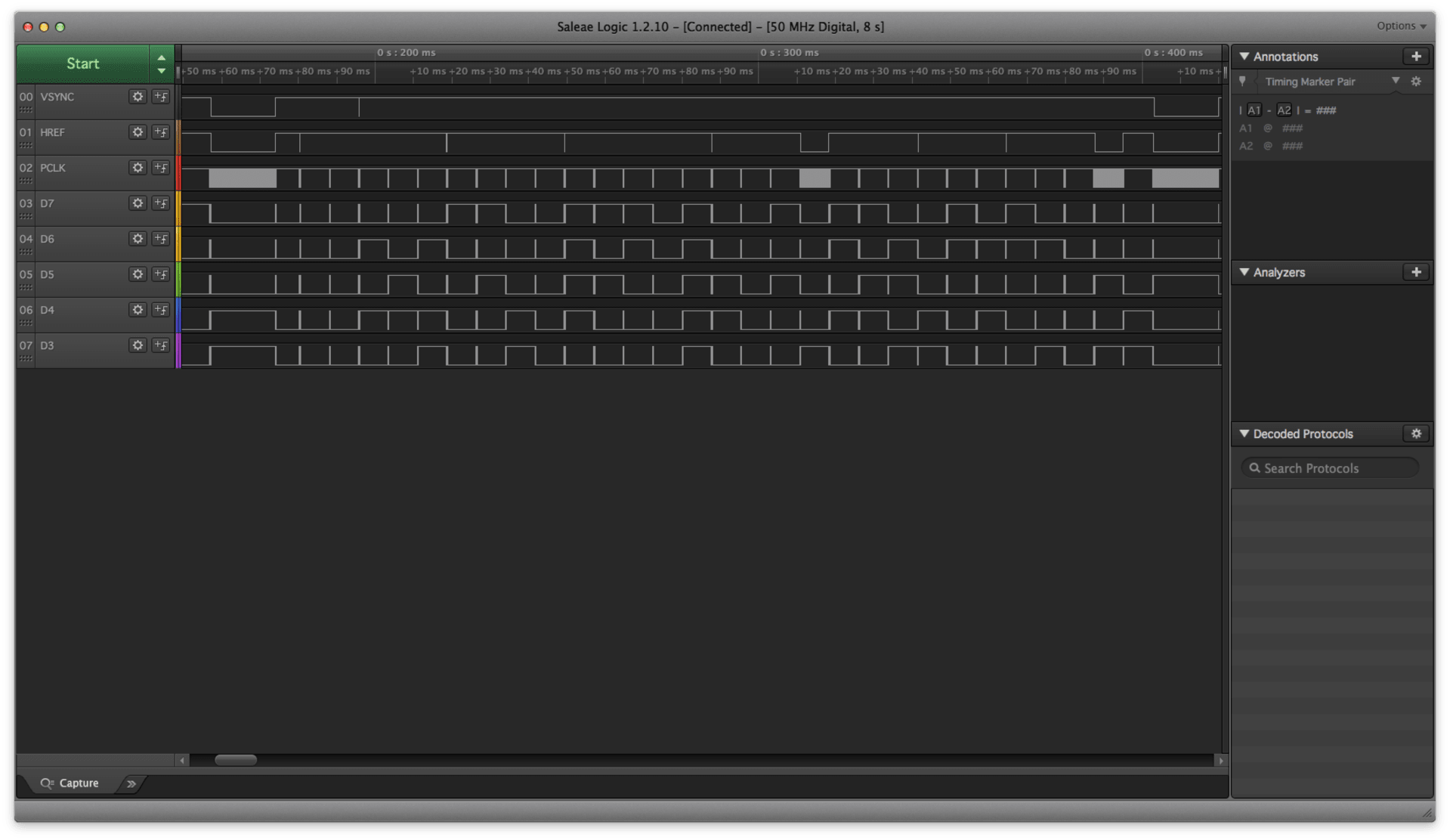

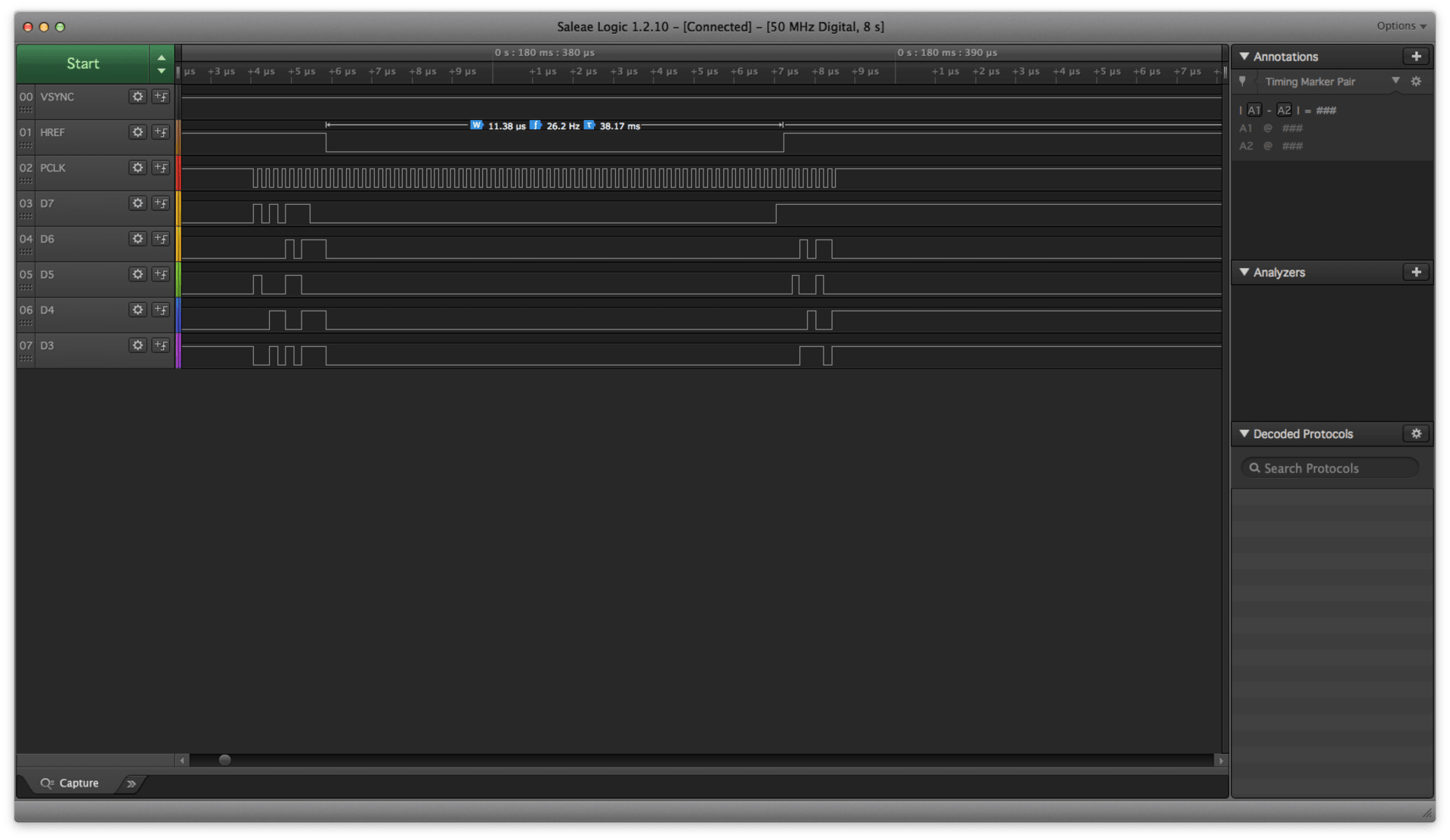

出力形式をJPEGに変更すると次のようになりました。

通常形式とは全く異なる、なんだかちょっと不思議なところもある信号です。

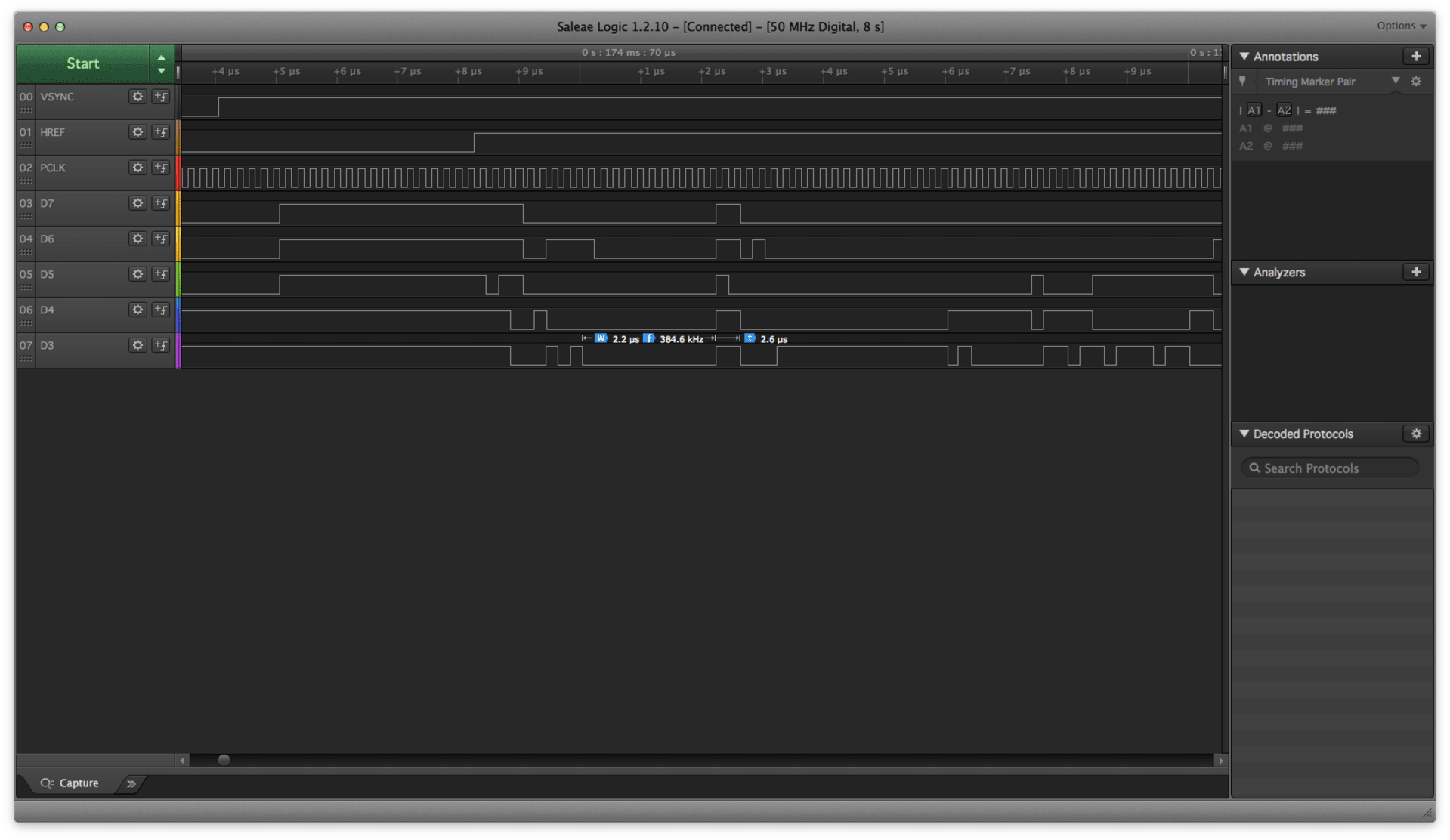

JPEG出力の始まりの部分をズームしてみると...

HREFが立ち上がって、すぐにSOI (0xFF, 0xD8) と APP0 (0xFF, 0xE0)がでているようです。

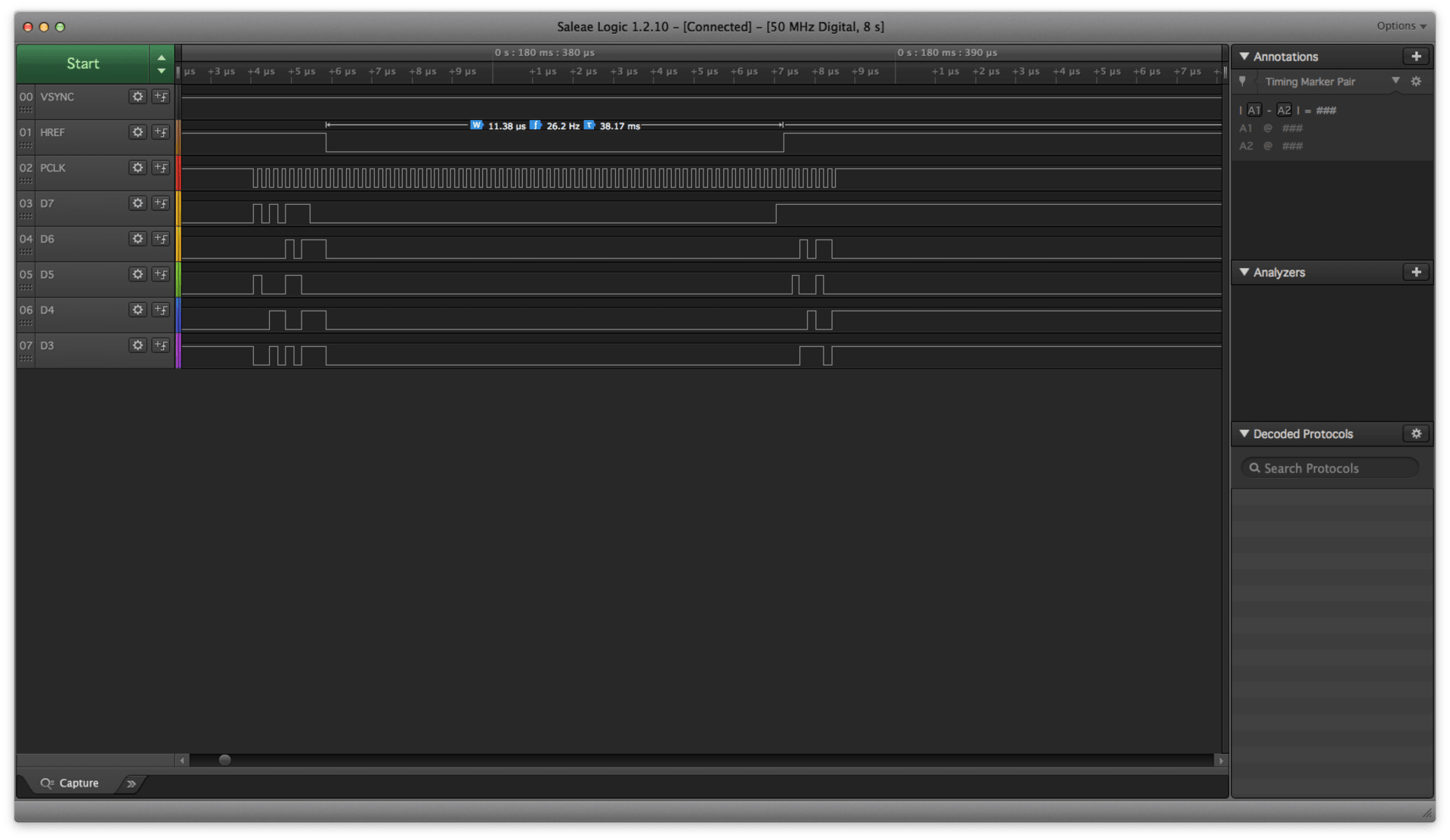

HREFでヒゲのように見えている部分も拡大してみると...

PCLKがしっかりと出ているので、この部分のデータは読み捨てなければいけないようです。GitHubにあった参考コードでは、HREFの変化を割り込みで検出してタイマーのキャプチャ動作を許可/禁止する仕掛けになっていましたが、PCLKの速度に比べてMCUのクロックが充分に早くないと処理が間に合いません。5MHzのPCLKでも画像がきちんと取得できなかったのは、これが原因ではないかと思われます。

HREFがLの期間のPCLKを無視するために、TIMERにはHREFとPCLKの論理積(AND)をとった信号を入れてやれば、問題を解決できるように思われます。

まずはJPEGモードではない、通常形式での出力の場合。

ひとつのVSYNC区間の間に、HREFがライン数回変化していることがわかります。PCLKは出っぱなし。

出力形式をJPEGに変更すると次のようになりました。

通常形式とは全く異なる、なんだかちょっと不思議なところもある信号です。

- VSYNCにはひとつヒゲが出ていますが、SYSCLKよりも短いようなので無視しても大丈夫そうです。

- HREFにもヒゲのように見える部分がありますが、こちらは10us程度の長さがあり、無視はできません。

- HREFがLの時にPCLKが続けて出ていますが、この時のデータは無視しなければいけないようです。

- HREFがHでもPCLKがでていない時の方が多い。

JPEG出力の始まりの部分をズームしてみると...

HREFが立ち上がって、すぐにSOI (0xFF, 0xD8) と APP0 (0xFF, 0xE0)がでているようです。

HREFでヒゲのように見えている部分も拡大してみると...

PCLKがしっかりと出ているので、この部分のデータは読み捨てなければいけないようです。GitHubにあった参考コードでは、HREFの変化を割り込みで検出してタイマーのキャプチャ動作を許可/禁止する仕掛けになっていましたが、PCLKの速度に比べてMCUのクロックが充分に早くないと処理が間に合いません。5MHzのPCLKでも画像がきちんと取得できなかったのは、これが原因ではないかと思われます。

HREFがLの期間のPCLKを無視するために、TIMERにはHREFとPCLKの論理積(AND)をとった信号を入れてやれば、問題を解決できるように思われます。