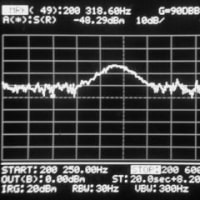

図73.(-3dB=4394kHz/nVout=243uV@20MHzRMS,87uV@900KHzRMS)

. 特に目新しい点は無いと思います

. 特に目新しい点は無いと思います

用途は600Ω出力の100KHzのOSC

にパッシブの18dB/octのLPFを付けて

10Vrmsを-140dB以下にして低Rzで

スタック測定回路をドライブしようとか

まあ計測アクセサリーの1つです暇人

の退屈しのぎ。

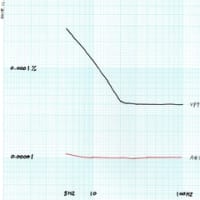

AD797は10Vの出力は目いっぱいで

VCCが18Vを0.2V切るとクリッピング点

に差しかかり歪は激増してしまいます

反対に18.02Vとなると図中の赤ライン10V/100KHzの歪が-125dBに減少します

わずか20mVがデッドライン!改良品を望みたいですねー、49860並みの22V型で。

OPA211なら12Vは可能ですが100Kの歪が797並みになるかが新たな課題...

因みに図の入力容量Ciを見るため47KΩの抵抗を介して信号加え-3dBのfrqで

逆算したらinput端子に付いている18pF分しかありません、靴の紐?効果です

この図を見て思いつくのがCas-Compにすぐ変化出来る..かも...と

訂正ic図の+とーを記入ミス .8

訂正ic図の+とーを記入ミス .8

. 特に目新しい点は無いと思います

. 特に目新しい点は無いと思います用途は600Ω出力の100KHzのOSC

にパッシブの18dB/octのLPFを付けて

10Vrmsを-140dB以下にして低Rzで

スタック測定回路をドライブしようとか

まあ計測アクセサリーの1つです暇人

の退屈しのぎ。

AD797は10Vの出力は目いっぱいで

VCCが18Vを0.2V切るとクリッピング点

に差しかかり歪は激増してしまいます

反対に18.02Vとなると図中の赤ライン10V/100KHzの歪が-125dBに減少します

わずか20mVがデッドライン!改良品を望みたいですねー、49860並みの22V型で。

OPA211なら12Vは可能ですが100Kの歪が797並みになるかが新たな課題...

因みに図の入力容量Ciを見るため47KΩの抵抗を介して信号加え-3dBのfrqで

逆算したらinput端子に付いている18pF分しかありません、靴の紐?効果です

この図を見て思いつくのがCas-Compにすぐ変化出来る..かも...と

訂正ic図の+とーを記入ミス .8

訂正ic図の+とーを記入ミス .8