CXMTはGAA構造を実装した次世代DRAMの試作品を開発した

(出所:CXMT)

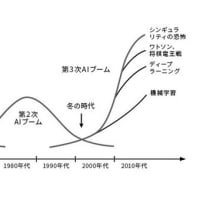

半導体の微細化や材料技術の発展を受けて、コンピューティング能力を高める新技術の開発が加速している。

半導体製造関連で世界最大級の国際会議「IEDM 2023」では、AI(人工知能)や量子コンピューティングで求められる半導体技術の発表が相次いだ。その中でも脚光を浴びていた3つの技術を紹介する。

①DRAMをGAAで微細化

中国のDRAMメーカーである長鑫存儲技術(CXMT)は、DRAM向けのGAA(ゲート・オール・アラウンド)トランジスタ構造を開発し、次世代DRAMへの実装に成功した。

GAAは最先端の半導体プロセスに使われており、次世代のコンピューターに欠かせない技術だ。

GAAを採用した量産品としては、韓国Samsung Electronics (サムスン電子)が3nm世代半導体の製造プロセスに初めて実装した。

台湾積体電路製造(TSMC)は、2025年からの量産を予定する2nm世代半導体で採用する計画だ。業界のトップランナーではないCXMTが、最先端のGAA技術をDRAMに適用したことで驚きが広がった。

CXMTは今回、メモリーセルを高密度化した「4F2」世代(メモリーセルの大きさを示す指標)のDRAMに搭載する、GAA垂直チャネルトランジスタ(VCT)セルアレイを作製した。

オンオフ比が優れており、サブスレッショルドスロープ(SS、トランジスタがオン状態に変化する際のドレイン電流が1桁増加するのに要するゲート電圧)値として62.5mV/decを達成した。

現在、微細化や3次元(3D)化による高性能化が検討されるDRAMだが、GAAの適用で一層の大容量化や省電力化が期待できる。

従来の6F2世代DRAMと比較したシミュレーションでは、各種タイミングパラメーター値や消費電力の点で優れた性能を示した。CXMTは「10nm世代以降の次世代DRAMを応用するためのマイルストーンになるだろう」と語った。

ただし、今回の開発はあくまで基礎研究であり、実際の生産プロセスへの応用は議論していない。この設計を採用した製品を市場に投入するには、まだ長い時間がかかる見込みだ。

今後、CXMTによるGAAトランジスタの開発は米中対立の影響を受ける可能性がある。最先端のGAAトランジスタを設計するには、欧米ベンダーが提供するEDA(電子設計自動化)ツールが必要だが、米国はこうしたEDAツールの対中輸出を規制している。

CXMTは今回使ったEDAツールの詳細を明らかにしていないが、今後も開発を続けられるかは不透明だ。

CXMTは現時点で米商務省の定めるエンティティーリスト(EL、禁輸リスト)に載っていないが、もし米中関係が悪化すれば欧米ベンダーのEDAツールを使えなくなり、研究開発を進められなくなる事態も考えられる。

②量子計算機の材料開発が進化

半導体の微細化の余地が狭まる中、将来は量子技術がコンピューターの発展を支えると期待されている。

IEDMでは量子コンピューターの性能を高める材料技術が複数紹介された。産業技術総合研究所(産総研)先端半導体研究センターの研究チームは、量子コンピューターを構成するトランジスタの極低温下でのスイッチング特性を解明する研究成果を発表した。

量子コンピューターの課題である量子ビットや制御回路のノイズを低減するのに役立つと期待する。

今回の研究では、1K(ケルビン)以下の極低温環境下で半導体界面の電子捕獲と呼ばれる現象がトランジスタのスイッチング特性を決定するメカニズムを「世界で初めて」(産総研)解明した。半導体界面の欠陥が捕獲する電子の量で、スイッチング特性を決めるというもの。産

総研はこの現象を、1K以下の環境下でのサブスレッショルド係数(S係数)の測定とシミュレーションの両面から特定した。

産総研は量子コンピューターのノイズ低減につながる極低温動作トランジスタの

スイッチング特性を解明した(出所:産総研)

同センター研究チーム長の森貴洋氏らは、今後1~2年ほどでノイズ低減技術を開発する計画だ。

特にシリコン型量子コンピューターで量子ビットのノイズを減らせば、コヒーレンス時間(量子情報の保持時間)を長くできることから、計算精度の改善と大規模化につなげたいと同氏は語る

量子コンピューター開発を支援する半導体製造装置メーカーなどと連携していく。

他にも、米University of California, Santa Barbara(カリフォルニア大学サンタバーバラ校、UCSB)やフランスCEA-Leti(フランス原子力・代替エネルギー庁電子情報技術研究所)、香港科技大学(HKUST)といった研究機関が、量子コンピューター向けの材料開発や設計技術の事例を紹介した。

半導体材料の知見を応用することで、計算エラーの原因となるノイズの減少や、高精度なシミュレーションが可能になり、量子コンピューターの早期実用化に役立つ見込みだ。

③半導体技術でニューロモルフィック開発

半導体の微細化が伸び悩む中、コンピューティング能力を高める技術開発が進む。そこで注目されているのが、人間の脳を模した「ニューロモルフィックコンピューティング」である。

イタリアUniversity of Pisa(ピサ大学)は、シリコン製CMOS(相補性金属酸化膜半導体)プロセスと2D材料技術を、アナログニューロモルフィック回路の製造に応用する研究を紹介した。試作したデバイスは優れた計算精度を持ち、将来は機械学習向けの専用チップとして利用できると期待する。

ニューロモルフィックコンピューティングは、機械学習の推論などを高速・低消費電力で処理できる特徴がある。

一般的なコンピューターは、メモリー回路と演算回路の間でデータをやり取りするが、微細化の限界や回路の発熱といった課題に直面しており、チップの根本的な変革が検討されるようになった。ニューロモルフィックコンピューティングは、こうした問題を解決する有効な手法になると期待されている。

キーワード

ゲート・オール・アラウンド(GAA)

電流が流れるチャネルの全周をゲートで囲み、チャネルの調整能力を高めたトランジスタの構造。

チャネルの周囲をゲートで囲むことで、リーク電流を抑えられる。3nm世代以降の先端半導体で採用されている。細長いシート状のチャネルを積み重ねたような「Nanosheet(ナノシート)」や、細いチューブ状のチャネルを縦に並べた「Nanowire(ナノワイヤ)」などの構造がある。

現在の半導体は、魚のフィン(ヒレ)を立てたような「FinFET」と呼ぶトランジスタ構造が主流だが、チャネルの全周を囲っていないのでリーク電流が生じてしまう課題があった。

日経記事 2024.02.02より引用