Rapidus(ラピダス)が2027年の量産開始に向けて製造を目指すのが、GAA(Gate All Around)という先端技術を使った2nm世代プロセスのロジック半導体である注1)。

GAA構造の量産に行きつける企業は、世界でも限られている。詳細を、トランジスタの基礎から順に追っていこう。

Q1:そもそもトランジスタはどう機能する?

Q2:何で集積化・微細化するの?

Q3:半導体チップはどんな構造?

Q4:半導体チップはどう作る?

Q5:EUV露光装置って何?

Q6:従来のプレーナFETは何が課題だった?

Q7:FinFETとは? どんなメリットがある?

Q8:日本がFinFETを量産できなかった技術的な難しさとは?

Q9:GAA構造とは? どんなメリットがある?

Q10:最先端のGAA構造はなぜ製造が難しい?

Q1 そもそもトランジスタはどう機能する?

ロジック半導体(IC)チップは入力された「0」または「1」の信号を演算することで動作する。この0または1の演算の根本にあるのがトランジスタである。トランジスタは簡単に言えばスイッチだ。このスイッチを何段にも組み合わせることによって複雑な演算を行っている。

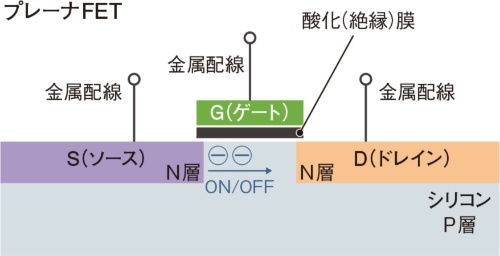

ロジック半導体で使われている「MOSFET(Metal-Oxide-Semiconductor Field Effect Transistor、金属酸化膜半導体電界効果トランジスタ)」と呼ばれるタイプのトランジスタを例にとろう(図1)。

ゲート電圧を印加すると、ソースからチャネルを通りドレインに電荷が移動する

(出所:日経クロステックが作製)

「ゲート(G)」と呼ばれる部分に、ある閾(しきい)値以上の電圧を与えるか、与えないかによって、「ソース(S)」と「ドレイン(D)」という部分に電流が流れる。

このゲートに電圧を印加するかどうかでドレイン-ソース間の電流をオン/オフできることがスイッチとなっているわけだ。

Q2 何で集積化・微細化するの?

半導体チップに含まれるトランジスタの数は膨大である。例えば、米Apple(アップル)の「iPhone 14 Pro Max」に搭載されているSoC(System on a Chip)†「A16 Bionic」には、約160億個のトランジスタを内蔵するとされる。

回路幅は、肉眼で見えないウイルスよりもさらに小さい。

では、なぜこのように微細化を進めるのか。

理由は主に4つ。

(1)コスト削減、

(2)低消費電力、

(3)動作速度向上、

(4)高機能化─である。

(1)として、トランジスタの製造コストを削減できる。1枚のウエハーに含まれるトランジスタが増えれば増えるほど、トランジスタ1個あたりの製造コストが下がる。

(2)(3)は、トランジスタが小さくなれば(正確にはゲート長が短くなれ)、オン/オフに必要とされる電子の個数および移動距離が小さくなるためである。小さな電力かつ素早い移動によって低消費電力、高速にできる。

(4)の高機能化は、微細化によりトランジスタを大量に配置し、これまで複数のチップで実現していた機能を1つのチップで実現できる。1つのチップ内に複数機能を盛り込めれば、(2)と(3)の理由によって、機能間の通信を高速化できるとともに、省電力化できる。

Q3 半導体チップはどんな構造?

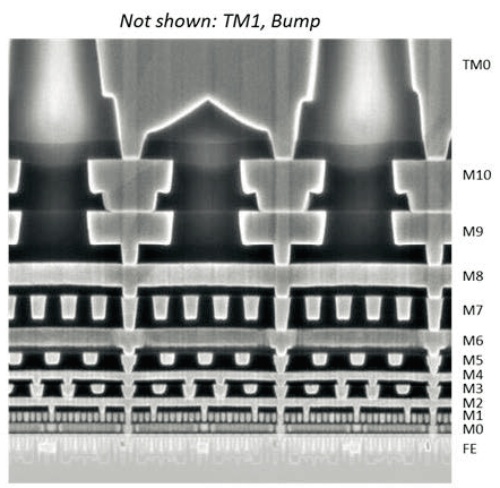

図2に示すのは、米Intel(インテル)が2017年に発表した10nm世代プロセス半導体チップの断面図である。

最下部付近(FE部分)にFinFETのトランジスタが配置されている。下部はトランジスタ工程(Front End Of Line、FEOL)、上部は配線工程(Back End Of Line、BEOL)と呼ばれる。

FEOLでは、シリコン(Si)基板上に、トランジスタや絶縁体となる酸化膜(SiO2)などを形成。BEOLで素子間を金属配線で接続する。

なお、BEOL部分は金属配線の層で構成するため、「メタル(M)層」とも呼ばれる。

このように金属配線を何層にも積み重ねるのは、論理回路を構成するためのトランジスタ同士を結ぶ配線のほか、チップの外部と信号や電力をやりとりできるレベルに配線の幅を拡大するという意味もある。

Q4 半導体チップはどう作る?

半導体製造はFEOLやBEOLで構成する前工程と、組み立てや検査などを担う後工程から成る。

前工程では、

(1)洗浄、

(2)成膜、

(3)露光、

(4)現像、

(5)エッチングといった工程の繰り返しを行っている。

まず、両面鏡面研磨のシリコン(Si)ウエハーを用意する。

次に、

(1)洗浄装置を使ってウエハーを洗浄。

(2)絶縁膜となるSiO2膜などを成長させながら積み上げていく。

(3)ウエハー表面に感光性樹脂(フォトレジスト)を塗布し、レーザー光を照

射。回路を焼き付けるパターン原版となるフォトマスクを光が通り、ウエ

ハー上に転写される(露光)。

(4)レジストの露光部分は薬液で溶かす。

(5)溶けた部分の下にある層を、薬品で溶かしたり、プラズマで削ったりして

回路をつくる。この作業を何度も繰り返すことで、回路が完成する。

BEOLで配線を経た後、後工程に移る。ウエハー上に形成した半導体チップを切断し、1チップずつ切り分ける。チップから信号線や電源線を取り出してパッケージ基板と接続するボンディング(接着)や、これらを樹脂などで封入するパッケージングを経て、IC製品が出来上がる。

Q5 EUV露光装置って何?

緻密な回路の露光には、より短い波長の光が必要になる。波長が短ければ短いほど、細かな線が描け、結果として半導体性能が向上するからである。この法則は「レイリーの式†」と呼ばれる。

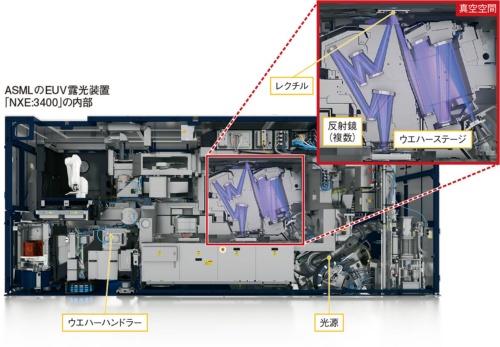

EUV(極端紫外線)露光装置は非常に緻密な露光を実現できるため、先端半導体の製造に欠かせない。波長が13.5nmとかなり短いからである。

前世代で現在主流の液浸ArF露光装置と比べると、波長を約10分の1にした。2023年2月時点では、開発を担うのはオランダASMLのみである(図3)。

EUV露光装置を使った露光の過程はこうだ。まず光源では、高速で落下するスズの粒に、2回に分けてレーザーパルスを照射。

スズがプラズマ状態になることで、EUV光が発生する。この工程は「1秒間に最大5万回」(ASML)実施する。

前世代の液浸ArF露光装置では、光をレンズに通して縮小投影し、微細なパターンを形成していた。ところが、EUV光はレンズをほぼ通過しない。そこで、複数のミラー(鏡)で代替している。

EUV光はミラーに反射しながら、高精細フォトマスクであるレチクルに到達する。レチクルで反射した光は、干渉によって回路パターンを伝達できる。反射鏡を使うことで、レチクルのパターンを4分の1に縮小してウエハーに露光できる。

なお、装置価格は1台数百億円と高い。納期も長く、ラピダスは同装置を2022年に発注し、「2024年末に導入できる見込み」(同社 代表取締役社長の小池淳義氏)と2年以上かかっている。

Q6 従来のプレーナFETは何が課題だった?

微細化が加速するにつれて、トランジスタの構造は変化を続けている。半導体チップを支えてきたのが「プレーナFET」である。

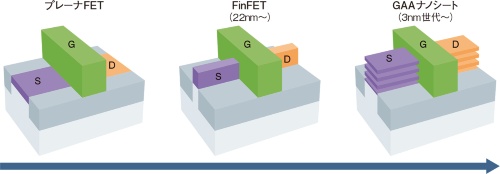

その後、22nmプロセス以降で「FinFET」、最先端の3nm 世代プロセスでGAAナノシートと、技術トレンドはめまぐるしく移り変わっている(図4)。

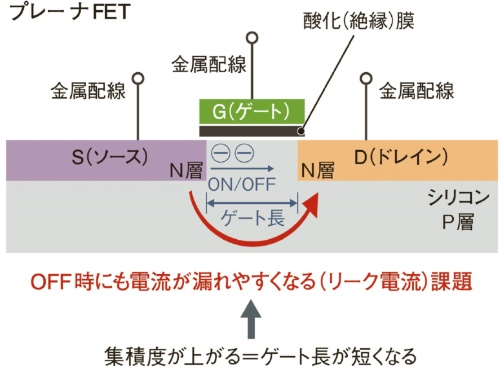

プレーナFETの課題は、オフ(絶縁時)時にもわずかに電流が漏れる(リーク電流)ことである。従来は無視できる程度だったものの、微細化が進むと急激に大きくなってしまう。「短チャネル†効果」と呼ばれる現象である(図5)。

微細化が進み、集積度が上がるとゲート長が短くなったり、酸化膜が薄くなったりしてしまう。オフ時に漏れる電流が無視できなくなるため、よりリーク電流を制御しやすい構造が必要だった(出所:日経クロステックが作製)

Q7 FinFETとは?どんなメリットがある?

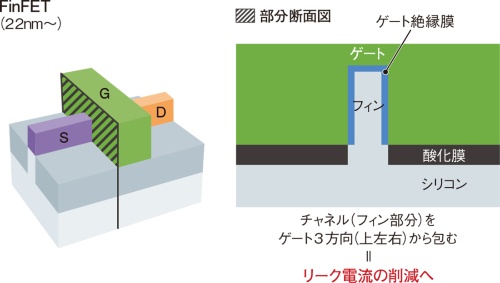

FinFET構造は、22nmプロセス以降のトランジスタで使われている。finとは英語で魚のヒレを指す。ソース―ドレイン間の電流経路であるチャネルが、ヒレのように突起しているためだ(図6)。

図6 リーク電流を抑えた「FinFET」

FinFETをプレーナFETと比べた主な利点は、チャネルを制御する面(方向)の数の違いにある。

プレーナFETは1面のみからチャネルを制御していたため、リーク電流が多かった。そこで、チャネルをゲートに食い込ませることで、3面から囲みリーク電流を抑制できた。

Q8 日本がFinFETを量産できなかった技術的な難しさとは?

FinFET構造は、実は日本企業が初めて作製に成功した技術である。日立製作所が1989年に開発を発表した。

ただ、商用生産にこぎつけたのは約20年後の2011年。その担い手は日本企業でなく、インテルだった。

FinFETの技術的な難しさはフィン部分の構造にある。縦に細長いチャネルを形成するためには、シリコン層をエッチングすることでフィン部分以外を取り除いている。この際に両側面をまっすぐにエッチングすることが難しい。

フィンの周囲には絶縁層やゲートを付加する必要があるが、ここがなめらかでない場合、こうしたものをうまく形成できないという問題もある。

フィンの幅をゲート長よりも短く加工する必要もあるため、プレーナ型より緻密である。構造が3次元的で複雑で、プレナー型に比べて製造にかかる工程も増え、設備も高度になるため、コストがかさむ。

上記のような課題から量産の歩留まりが問題となり、製造につなげにくかった。

Q9 GAA構造とは?どんなメリットがある?

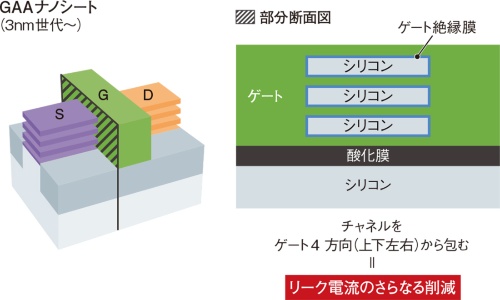

GAAとは、「ゲート全方向(Gate All Around)」という名の通り、ゲートが全方向からチャネルを包み込む構造をしている。

トランジスタとしてはMOSFETのため、そのトランジスタ構造はFinFETという呼び方に準じて「GAA FET」と呼ばれる。

FinFETとの大きな違いは、3面から4面にチャネルの制御面の数を増やしたこと。具体的には、FinFETのチャネルを90°回転し、縦に積層。リーク電流をさらに抑えられるようにした(図7)。

GAA FETでは、チャネルの周囲全方向(All Around)をゲートが囲む構造を実現。リーク電流をFinFETよりさらに抑えて高効率を実現している。

なお、酸化(絶縁)膜部分の加工は「Bottom Dielectric Isolation(BDI、底面絶縁膜)」と呼ばれる手法を使う(出所:日経クロステックが作製)

GAAナノシートは、薄く伸ばしたチャネルを縦に複数枚積み重ねたGAA構造である。

「基本的に積層する枚数が多いほど性能は向上する」と東京大学 生産技術研究所 情報・エレクトロニクス系部門 教授の平本俊郎氏は説明する。

なお、GAA FETの量産技術は世界でも萌芽(ほうが)したばかり。韓国Samsung Electronics(サムスン電子)は2022年7月、3nm世代プロセスのGAAナノシートを量産開始したと発表している。

対する台湾TSMC(台湾積体電路製造)は、GAAナノシートの「N2」を2025年に量産開始する見込みで、サムスン電子を追う。

また、インテルも、同社初のGAAトランジスタプロセス「Intel 20A」での生産を2024年上期に、その改良版の「Intel 18A」での生産を2024年下期に開始すると発表している。

Q10 最先端のGAA構造はなぜ製造が難しい?

「GAA FETの製造の難しさは、3次元的に考えなければならない部分が多いこと」。平本氏はこう説明する。

GAA FETの基本的な製造方法はこうだ。まず、Siとシリコンゲルマニウム(SiGe)を交互に積層した上で、FinFETのような突起型の構造を形成する。SiGeは特殊な溶剤で溶かすことができるため、SiGeをエッチングすればSiのみが残る仕組みである。

この際、課題になるのがナノシートの下に位置するSi層である。このSiの層がソースとドレインの間に挟まれるために、新たに意図しないチャネルが形成され、電流が漏れて効率低下につながってしまう。

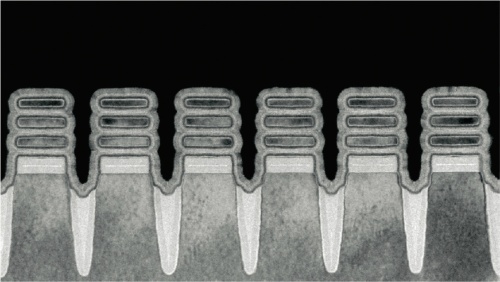

そこで、米IBMなどはこのSi層とナノシートの間に絶縁膜(SiO2)を形成する技術を発表している。「Bottom Dielectric Isolation(BDI、底面絶縁膜)」と呼ばれる手法である(図8)。

図8 IBMが発表した2nm GAAナノシートの断面

さらに、チャネル周囲にゲートとナノシートとを絶縁するために「サイドウォールスペーサー」が必要になるなど、FinFETと比べても製造はかなり複雑になる。そのため、実用化に2022年まで至らなかった経緯がある注2)。

ラピダスは、この複雑な構造を量産できる手法を確立する必要がある。

https://blog.goo.ne.jp/admin/entries?ymd=&category_id=863afcc284ad7e9435b8d005d847a1ec#block1