JP5696081

本実施形態において、画素は、フォトダイオードを用いて形成される。1つのフォトダイオードは、1つの画素に対応する。例えば、画素としてのフォトダイオード1を用いて、CMOSセンサ又はCCDセンサが形成される。

ここで、図5を用いて、画素アレイ120の内部構成の一例について説明する。図5は、画素アレイ120及びその近傍の回路の回路構成例を示す図である。

複数の単位セル20は、画素アレイ120内に、マトリクス状に配置されている。各単位セル20は、制御線TRF,RST,ADRと信号線VSLとの交差位置に、設けられている。

単位セル20は、例えば、フォトダイオード1及びフォトダイオード1の動作を制御する回路(素子)を含む。単位セル20のフォトダイオード1の動作を制御する回路は、例えば、4つの電界効果トランジスタ2,3,4,5によって形成される。各電界効果トランジスタ2,3,4,5は、例えば、nチャネル型MOSトランジスタである。以下では、単位セル20に含まれる4つの電界効果トランジスタのことを、トランスファゲート(リードトランジスタ)2、アンプトランジスタ3、リセットトランジスタ4及びアドレストランジスタ5とそれぞれよぶ。

フォトダイオード1を含む単位セル20において、フォトダイオード1に入射した光(被写体からの光)の光量に応じて、フォトダイオード1内部に電荷が発生する。フォトダイオード1は発生した電荷を蓄積できる。

フォトダイオード1のカソードは、トランスファゲート2の電流経路を介して、信号検出部としてのフローティングディフュージョン(浮遊拡散層)6に接続されている。

トランスファゲート2は、フォトダイオード1の信号電荷の蓄積及び放出を制御する。トランスファゲート2のゲートは読み出し制御線(読み出し信号線)TRFに接続されている。トランスファゲート2の電流経路の一端はフォトダイオード1のカソードに接続され、トランスファゲート2の電流経路の他端はフローティングディフュージョン6に接続されている。

トランスファゲート2がオフ状態である場合、フォトダイオード1における電荷の蓄積状態が維持される。トランスファゲート2がオン状態である場合、フォトダイオード1に蓄積された電荷が、オン状態のトランスファゲート2のチャネルを経由して、フローティングディフュージョン6に出力される。

アンプトランジスタ3は、フローティングディフュージョン6の保持する信号(フローティングディフュージョン6の電位)を増幅する。アンプトランジスタ3のゲートは、フローティングディフュージョン6に接続されている。アンプトランジスタ3の電流経路の一端は垂直信号線VSLに接続され、アンプトランジスタ3の電流経路の他端はアドレストランジスタ5の電流経路の一端に接続されている。アンプトランジスタ3によって増幅された信号は、垂直信号線VSLに出力される。アンプトランジスタ3は、そのゲートに印加されるフローティングディフュージョン6の電位の大きさに応じて駆動する。アンプトランジスタ3は、単位セル20内において、ソースフォロワとして機能する。

図4に示されるように、フォトダイオード1は、画素アレイ120の単位セル20の形成領域(以下では、単位セル形成領域20とよぶ)において、半導体基板(又は半導体層)30内に形成される。フォトダイオード1は、半導体基板30内に形成された少なくとも1つの不純物層(不純物半導体層、不純物半導体領域)10から形成される。フォトダイオード1の少なくとも1つの不純物層10は、N型の導電型を有する。但し、フォトダイオード1の特性(例えば、感度)を向上させるために、導電型及び不純物濃度が異なる複数の不純物層によって、フォトダイオード1が形成されてもよい。フォトダイオード1によって光電変換された入射光の光量に応じた電荷は、フォトダイオード1の不純物層10内に発生し、不純物層10内に蓄積される。

例えば、フォトダイオード1の不純物層10の表層(上面)において、P型の導電型の不純物層(以下では、表面シールド層とよぶ)11が設けられている。表面シールド層11は、半導体基板30を覆う層間絶縁膜90に起因する不純物(例えば、炭素又は窒素)が、フォトダイオード1内に拡散するのを、抑制する。表面シールド層11によって、不純物に起因したフォトダイオード1の特性の劣化、例えば、暗電流の発生が、抑制される。

半導体基板30の半導体領域(例えば、P型の半導体領域)38内に、フローティングディフュージョン6としての不純物層60が、設けられている。フローティングディフュージョン6の不純物層60は、例えば、N型の導電型を有する。フローティングディフュージョン6としての不純物層60内に、フォトダイオード1からトランスファゲート2を経由して出力された電荷が、保持(蓄積)される。

フォトダイオード1とフローティングディフュージョン6との間において、トランスファゲート2が、半導体基板30上に設けられている。トランスファゲート2のゲート電極22は、ゲート絶縁膜21を挟んで、半導体基板30のP型不純物領域(以下、P型領域と表記する)38上に設けられる。例えば、半導体領域38内に形成された不純物層(図示せず)が、トランスファゲート2のソース及びドレインとして用いている。フォトダイオード1が含む不純物層、又は、フローティングディフュージョン6としての不純物層が、トランスファゲート2のソース及びドレインとして用いられてもよい。

素子分離領域9A内に設けられた素子分離層98が、隣接する単位セル20及び隣接するフォトダイオード1を取り囲むように、半導体基板30内に設けられている。素子分離層98によって、互いに隣接する単位セル20及びフォトダイオード1が、電気的に分離される。画素アレイ120内の素子分離層98は、例えば、不純物層(以下では、素子分離不純物層とよぶ)によって、形成される。素子分離層としての不純物層98は、例えば、P型の導電型を有している。尚、画素アレイ120内における素子分離層98は、STI構造の絶縁膜(素子分離絶縁膜)によって、形成されてもよい。

周辺回路領域125A,125B内には、例えば、図5のAD変換回路131や垂直シフトレジスタ133などの回路が、設けられている。

周辺回路領域125A,125Bは、例えば、素子分離領域9Bによって、画素アレイ120から電気的に分離されている。周辺回路領域125A,125Bを区画するための素子分離領域9B内には、例えば、STI構造の素子分離絶縁膜99が埋め込まれたり、素子分離不純物層31B,98が設けられたりしている。

例えば、周辺回路領域125Aがアナログ回路領域である場合、P型不純物領域(P型領域)31Aが、アナログ回路領域125Aの半導体基板30内に、設けられている。例えば、P型領域31Aは、接地電位(グランド電位)が印加される金属層(図示せず)に接続されている。例えば、周辺回路領域125Bがロジック回路領域である場合、N型不純物領域(以下では、N型領域と表記する)32が、ロジック回路領域125Bの半導体基板30内に、設けられている。ロジック回路領域125Bにおいて、N型領域32の周囲を取り囲むように、P型領域31Bが設けられている。周辺回路領域125A,125BのP型領域31A,31Bは、半導体基板30の第1の面から第2の面へ達するように、形成されている。

P型及びN型のウェル領域39が、アナログ回路領域125AのP型領域31内、及び、ロジック回路領域125BのN型領域32内に、それぞれ設けられている。ウェル領域39内に、電界効果トランジスタ、抵抗素子、又は、容量素子などの、イメージセンサ100の周辺回路の構成素子が、設けられている。図4には、周辺回路の構成素子としての電界効果トランジスタ7が示されている。

アナログ及びロジック回路領域125A,125B内において、電界効果トランジスタ(例えば、MOSトランジスタ)7は、ウェル領域39内に設けられている。ウェル領域39内に、トランジスタ7のソース/ドレインとしての2つの不純物層(拡散層)73が設けられている。2つの拡散層73間のウェル領域39表面に、ゲート絶縁膜71を介して、ゲート電極72が設けられる。2つの拡散層73間のウェル領域39が、トランジスタのチャネル領域となる。電界効果トランジスタ7が、Pチャネル型であるかNチャネル型であるか、或いは、エンハンスメント型であるかデプレッション型であるかは、電界効果トランジスタ7が設けられるウェル領域39の導電型、或いは、ソース/ドレインとしての不純物領域(拡散層)73の導電型に応じる。

尚、上述の例では、アナログ回路領域125A内のP型領域31A及びロジック回路領域125B内のN型領域32を示しているが、アナログ回路領域125AがN型領域を含む場合もあるし、ロジック回路領域125BがP型領域を含む場合もある。

トランジスタ2,7のゲート電極22,72及びフォトダイオード1の上面(表面シールド層11)を覆うように、複数の層間絶縁膜90が、半導体基板30上に積層されている。層間絶縁膜90には、例えば、シリコン酸化膜が用いられる。

US9006807(JP)

[0069] A plurality of interlayer insulating films 90 are stacked on the semiconductor substrate 30 to cover the upper surfaces (the surface shield layer 11 ) of the gate electrodes 22 and 72 of the transistors 2 and 7 and the photodiode 1 . For example, a silicon oxide film is used for the interlayer insulating films 90 .

本実施形態のイメージセンサ100に対して、多層配線技術が用いられている。すなわち、各配線レベル(基板表面を基準とした高さ)に応じて、複数の導電層91が、積層された層間絶縁膜90内にそれぞれ設けられている。導電層91は、層間絶縁膜90内のそれぞれに埋め込まれたプラグ92によって、上方又は下方の配線レベルに位置する他の導電層91に、電気的に接続されている。導電層91は、例えば、銅(Cu)又はアルミニウム(Al)を含む金属層である。例えば、銅(又は銅合金)からなる導電層91は、ダマシン構造を有し、層間絶縁膜90内に形成された溝内に、埋め込まれている。

例えば、トランジスタ2,7のゲート電極22,72、ソース/ドレイン73、及び、半導体基板30上に形成された素子の端子は、コンタクトプラグ92を介して、半導体基板30側から数えて1番目(最下層)の配線レベルに位置する導電層(配線)91に接続される。各層間絶縁膜90内の導電層91が、プラグ92を介して、上層(又は下層)の配線レベルの導電層91に接続されることによって、半導体基板30上に設けられた複数の素子が、互いに接続される。これによって、イメージセンサ100が含む複数の回路が形成される。

尚、導電層91は、素子間及び回路間を接続する配線に加え、素子及び回路に接続されないダミー層、フォトダイオードに対する光の入射を防止する遮光膜を含む。

最上層の層間絶縁膜90上に、支持基板85が設けられている。支持基板85は、例えば、接着層(保護層、平坦化層)88を介して、層間絶縁膜90上に積層される。支持基板85には、例えば、シリコン基板や絶縁性基板が用いられる。支持基板85によって、裏面照射型イメージセンサ100が支持されている。

再配線技術によって形成された配線(図示せず)が、支持基板85と層間絶縁膜90との間に、設けられてもよい。以下では、再配線技術によって形成された配線のことを、再配線(Re-Distribution Layer)とよぶ。

ここで、本実施形態において、素子が形成された面、より具体的には、トランジスタ2,7のゲート電極22,72が設けられている半導体基板30の面(第1の面)を半導体基板30の表面とよぶ。半導体基板30の表面上には、多層配線技術によって形成された層間絶縁膜90が設けられている。本実施形態において、半導体基板30の表面に対向する面(第2の面)を、半導体基板30の裏面とよぶ。図3は、イメージセンサを裏面側から見た場合の平面構造を模式的に示している。尚、半導体基板30の表面と裏面とを区別しない場合には、主面とよぶ。

本実施形態において、図4に示されるように、半導体基板30の裏面側に、平坦化層89を介して、カラーフィルタ層CFが設けられる。平坦化層89は、保護層及び接着層としての機能を有する絶縁膜である。

カラーフィルタ層CFは、半導体基板30の主面(表面及び裏面)に対して垂直方向に関して、画素アレイ120と重なる位置に、設けられている。例えば、単板式のイメージセンサは、単一の画素アレイ120で複数の色情報を取得する。この場合、カラーフィルタ層CFは、1つの画素(フォトダイオード1)に対して、例えば、赤(R)に対応する波長域の光を透過するフィルタ(色素膜ともよばれる)、緑(G)に対応する波長域の光を透過するフィルタ及び青(B)に対応する波長域の光を透過するフィルタを含み、赤、青及び緑のうち少なくとも1色のフィルタが、1つのフォトダイオード1(又は単位セル20)に対応するように、設けられている。

カラーフィルタ層CFの各フィルタが、所定のパターンを有するように、配列されている。尚、カラーフィルタ層CFは、赤、緑及び青に加え、黄(Y)に対応する波長域の光を透過するフィルタ、又は、可視光の全波長域を透過させる白(W)のフィルタを有してもよい。カラーフィルタ層CFは、例えば、ベイヤー配列やWRGB配列などの所定の配列パターンを有する。

マイクロレンズアレイMLは、保護層(図示せず)及び接着層(図示せず)を介して、カラーフィルタ層CF上に取り付けられている。

マイクロレンズアレイMLは、半導体基板30の主面に対して垂直方向に関して、カラーフィルタ層CFを介して、画素アレイ120上方に設けられている。マイクロレンズアレイMLは、1つの画素(フォトダイオード1)にそれぞれ対応するマイクロレンズが、2次元に配列されることによって、形成されている。各マイクロレンズは、各画素1に対して入射光を集光する。尚、マイクロレンズML及びカラーフィルタCFを取り付けるための接着層/保護層(平坦化層89)は、入射光に対して透過性を有する。

マイクロレンズアレイMLが取り付けられた面は、半導体基板30の裏面である。素子が形成された半導体基板30は、層間絶縁膜90とマイクロレンズアレイMLとに挟まれている。このように、本実施形態のイメージセンサ100において、マイクロレンズアレイML及びカラーフィルタ層CFは、トランジスタ2,7のゲート電極22,72及び層間絶縁膜90が設けられた面(表面)とは、反対側の面(裏面)に設けられている。被写体からの光は、マイクロレンズアレイML及びカラーフィルタ層CFを経由して、半導体基板30の裏面側から画素アレイ120に照射される。

本実施形態のイメージセンサ100のように、素子が形成された半導体基板30の表面に対向する裏面からの光がフォトダイオードに照射される構造のイメージセンサのことを、裏面照射型イメージセンサとよぶ。

例えば、半導体基板30の裏面側に、単位セル20Xを覆う遮光膜81Xが、設けられている。画素アレイ120内における遮光膜81Xに覆われた領域129は、オプティカルブラック領域(以下、OB領域又は遮光領域と表記する)129である。OB領域129内の単位セル20Xによって、図5の電源端子135に印加される基準電位、又は、有効領域129内の単位セル20における暗電流の補正のための電位(又は電流)が、生成される。以下では、画素アレイ120内のOB領域129以外の領域121のことを、有効領域121とよぶ。

例えば、OB領域129において、対応する色の異なる複数のフィルタの積層膜CFXが、遮光膜81Xと上下と重なる位置に積層されている。これによって、OB領域129に対する遮光性が向上される。複数のフィルタの積層膜が、OB領域129内に設けられている場合、遮光膜81XがOB領域129内に設けられなくともよい。尚、OB領域129において、マイクロレンズMLが形成されなくともよい。

例えば、半導体基板30の裏面側において、画素アレイ120の半導体基板30内に、シールド層としての不純物層19が設けられている。半導体基板30の裏面側のシールド層(以下、裏面シールド層とよぶ)19は、マイクロレンズアレイMLと半導体基板30との間に設けられた各層89,81X,CFに起因する不純物が、半導体基板30内に拡散するのを抑制する。これによって、基板30の裏面側からの不純物の拡散に起因した単位セル20の構成要素2,3,6の特性の劣化が、抑制される。

半導体基板30の表面側に設けられたパッド及び半導体基板30の裏面側に設けられたパッド81,81Aによって、イメージセンサ100と外部装置との間において信号が入出力されたり、イメージセンサ100に電圧が供給されたりする。

例えば、最上層の層間絶縁膜90内の導電層(配線)91、又は、最上層の層間絶縁膜90上の再配線(図示せず)、又は、支持基板85上(又は内部)の金属層(図示せず)が、半導体基板30の表面側のパッドとして、用いられる。以下では、イメージセンサが形成される半導体基板30の表面側に設けられるパッドのことを、表面側パッドとよぶ。尚、裏面照射型イメージセンサにおいて、表面側パッドを設けずともよい。

図3及び図4に示されるように、半導体基板30の端部(半導体基板30の外周部)に、複数のコンタクト領域180が設けられている。コンタクト領域180は、例えば、画素アレイ120及び周辺回路領域125A,125Bに隣接する。図3において、コンタクト領域180が、画素アレイ120と周辺回路領域125A,125Bとが隣接する方向における半導体基板30の一端及び他端に設けられた例が示されている。但し、イメージセンサ100のチップ内のレイアウトに応じて、コンタクト領域180が、画素アレイ120と周辺回路領域125A,125Bとが隣接する方向と交差する方向おける半導体基板30の一端及び他端に設けられる場合もあるし、画素アレイ120及び周辺回路領域125A,125Bを取り囲むように、四角形状のチップの各辺に沿って設けられる場合もある。

コンタクト領域180,180Aは、半導体基板30内において、P型又はN型の不純物領域31Bを含んでいる。半導体基板30の主面に対して垂直方向から見て、コンタクト領域180は、四角形状の平面形状を有し、例えば、長方形状の平面形状を有している。コンタクト領域180内において、TSV(Through Silicon Via)技術によって、半導体基板30の表面側から裏面側に向かって半導体基板30を貫通するように、貫通孔(開口部)T1が、半導体基板30内に形成される。

その貫通孔T1内に、貫通電極(貫通ビアともよばれる)83が埋め込まれる。貫通孔T1の側面(側壁)上に、絶縁膜(図示せず)が設けられ、貫通電極83は、絶縁膜によって、半導体基板30から電気的に分離されている。貫通電極83は、層間絶縁膜90内のプラグ92を経由して、層間絶縁膜90内の導電層91に接続される。本実施形態のイメージセンサ100において、各コンタクト領域180,180A内において、1つ又は複数の貫通電極83及び1つ又は複数の貫通孔が設けられる。

半導体基板30の裏面側において、1つのパッド81,81Aが、例えば、1つのコンタクト領域180に対応するように、それぞれ設けられている。パッド81,81Aは、例えば、四角形状の平面形状を有している。

1つのパッド81,81Aは、コンタクト領域180,180A内に設けられた1つ又は複数の貫通電極83に接続される。パッド81,81Aと半導体基板30の裏面との間には、絶縁膜(図示せず)が設けられ、パッド81,81Aは、その絶縁膜によって、半導体基板30から電気的に分離されている。

パッド81,81Aは、貫通電極83及び層間絶縁膜80内のプラグ92を介して、半導体基板30の表面側の導電層(配線91)に接続される。以下では、イメージセンサが形成される半導体基板の裏面側に設けられるパッド81,81Aのことを、裏面側パッド81,81Aとよぶ。

裏面側パッド81,81Aの平面形状は、正方形状でもよいし、長方形状でもよい。また、裏面側パッド81,81Aの平面形状は、四角形の角が欠けた形状でもよい。

例えば、駆動電圧Vdd又はグランド電圧(接地電圧)Vssをイメージセンサに印加するための電源パッド、信号の入出力用のパッドが、テストピン又はモニターピンに接続されるパッドなどが、表面側パッド及び裏面側パッド81,81Aとして用いられる。

貫通電極83は、高濃度の不純物を含む半導体(例えば、ポリシリコン)を用いて、形成される。裏面側パッド81,81Aは、金属層(例えば、アルミニウム)を用いて形成される。例えば、裏面側パッド81,81Aは、遮光膜81Xと実質的に同時に形成され、同じ材料(例えば、アルミニウム又は銅)からなる。貫通電極83は、金属を用いて、形成されてもよい。

複数の裏面側パッド81,81A及びコンタクト領域180は、イメージセンサ100のチップ30の各辺に沿って、配列されている。以下では、チップの各辺における裏面側パッド81,81Aが配列される方向のことを、パッド配列方向とよぶ。

半導体基板30の外周、例えば、コンタクト領域180,180A内において、ガードリング(図示せず)が、半導体基板30内に設けられた溝(又は貫通孔)内に設けられている。

JP2014022561

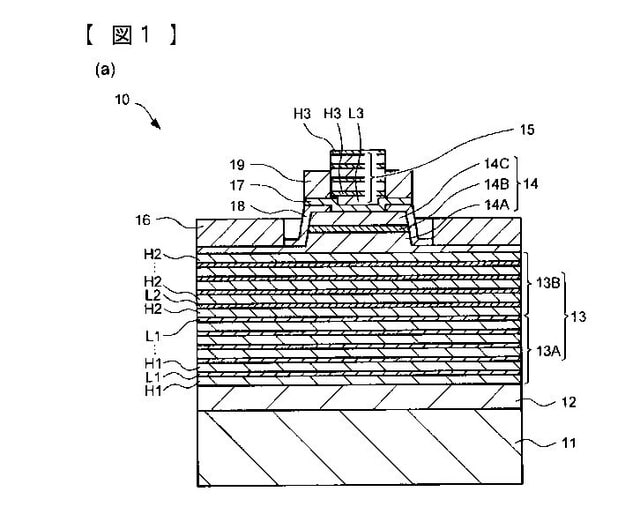

[0015] [画素部構造:断面構成]

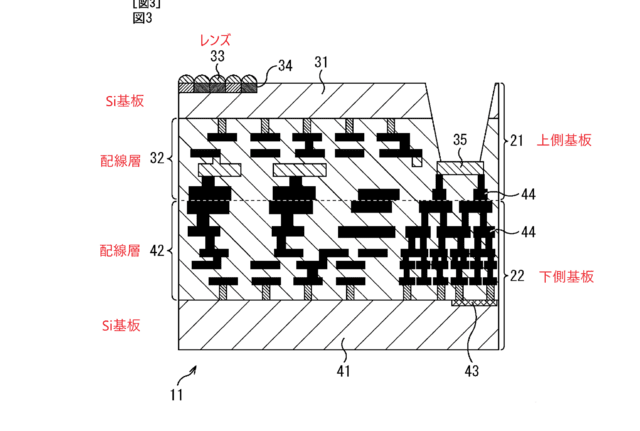

次に、図3に、図2に示す画素部のA−A線断面の構成を示す。

図3に示すように、固体撮像装置は、センサ基体3(第1半導体基体)と回路基体9(第2半導体基体)とが、それぞれ第1配線層31と第2配線層41を対向させて貼り合わされている。また、センサ基体3と回路基体9との貼り合わせ面において、センサ基体3の第1配線層31の表面に形成された第1電極35と、回路基体9の第2配線層41の表面に形成された第2電極45とが接合されている。

[0016] センサ基体3には、上述の図2に示すフォトダイオードPD1,PD2と、フローティングディフュージョンFDと、転送ゲート電極21,22が形成されている。センサ基体3は、図の上方が光の入射面であり、下方が回路形成面である。フローティングディフュージョンFDと転送ゲート電極21,22は、センサ基体3の回路形成面側に形成されている。

[0017] センサ基体3の回路形成面上には、第1配線層31が形成されている。第1配線層31は、少なくとも1層以上の配線と、絶縁層とが積層された構成を有する。図3では、1層の配線33を有する構成である。第1配線層31には、フローティングディフュージョンFDに接続されるプラグ32が形成されている。そして、プラグ32と配線33とが接続し、さらに配線33とプラグ34とが接続されている。

なお、配線33と同じ層に、図示しない他の配線を有している。この配線33と同じ層の配線は、例えば、転送ゲート電極21,22と接続される電源配線やグランド配線等である。

第1配線層31の表面には、接続用の第1電極35が形成されている。第1電極35は、プラグ32,34及び配線33を介してフローティングディフュージョンFDに接続されている。

[0018] 回路基体9には、図示しない画素部の制御回路や、信号処理回路を含むロジック回路が搭載されている。また、回路基体9には、転送トランジスタTr1の以外の画素トランジスタが形成される。図3では、増幅トランジスタTr5と選択トランジスタTr6を示している。回路基体9の表面には、増幅トランジスタTr5と選択トランジスタTr6のソース/ドレインとなる拡散領域27,28,29が形成されている。また、回路基体9上に増幅ゲート電極25と、選択ゲート電極26とを備える。

[0019] 回路基体9上には、第2配線層41が形成されている。第2配線層41は、複数層の配線と絶縁層とが積層された構成を有する。図3では、第2配線層41に形成される複数の配線のうち、1層の配線43,47を示している。配線43は、プラグ42,44により、増幅ゲート電極25と、第2配線層41の表面の第2電極45とに接続されている。このため、第2電極45は、プラグ42,44及び配線43を介して増幅ゲート電極25に接続されている。

また、選択トランジスタTr6の拡散領域29には、プラグ46と配線47とが接続されている。

[0020] 上述の構成では、センサ基体3の表面に設けられたフローティングディフュージョンFDと、回路基体9上に設けられた増幅ゲート電極25とが、第1電極35と第2電極45を介して導体により直接接続されている。つまり、フローティングディフュージョンFDと増幅ゲート電極25とが、第1電極35、第2電極45、プラグ32,34,42,44及び配線33,43からなるフローティングディフュージョン配線(以下、FD配線)により接続されている。

このように、センサ基体3のフローティングディフュージョンFDに蓄積された信号を処理するための画素トランジスタが回路基体9に形成されている。

[0021] 第1配線層31において、FD配線を構成する第1電極35、プラグ32,34及び配線33は、変換効率を上げるために、最小デザインルール配線幅で形成されることが好ましい。また、フローティングディフュージョンFDから第1電極35までは、同じく変換効率を上げるために、最短で結線されていることが好ましい。さらに、このプラグ32,34及び配線33は、第1配線層31に形成される他の配線と容量結合しないように、可能な限り他の配線との距離を離して形成することが好ましい。

同様に、第2配線層41において、FD配線を構成する、第2電極45、プラグ44,42及び配線43は、変換効率を上げるために、最小デザインルール配線幅で形成されることが好ましい。また、増幅ゲート電極25から第2電極45までは、変換効率を上げるために、最短で結線されていることが好ましい。さらに、このプラグ44,42及び配線43は、第2配線層41に形成される他の配線と容量結合しないように、可能な限り他の配線との距離を離して形成することが好ましい。

[0022] また、図示しないリセットトランジスタは、センサ基体3側において、画素共有単位間に形成されていてもよく、回路基体9側の他の部分に形成されていてもよい。センサ基体3のフォトダイオードPDの面積を大きくするためには、転送トランジスタ以外の各トランジスタは、すべて回路基体9側に形成されていることが好ましい。

[0023] 第1電極35及び第2電極45を形成する領域37は、増幅トランジスタTr5を共有する複数のフォトダイオードPD1〜4が形成されている領域36の面積よりも小さい構成とする。隣接する他の領域の電極との接触を避けるため、第1電極35及び第2電極45をフォトダイオードPD1〜4が形成されている領域36よりも、小さくする必要がある。

また、第1電極35及び第2電極45との少なくとも一方は、フローティングディフュージョンFDが形成されている面積よりも大きく形成されることが好ましい。

なお、上述の図2において、第1電極35及び第2電極45を形成する領域37の平面配置を破線で示している。