A.C.さんにクロック同期設計を教えていただいて、

髭を剃りました。

綺麗、綺麗!

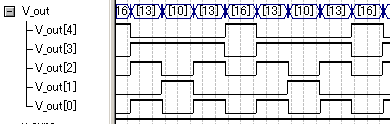

最終出力部分をこんな風に一旦FFに入れておいて、

クロック毎のエッヂで出力するかんじです。

-- calculate V-out

process (C_signal,Y_signal)

begin

Vout_tmp <= Y_signal + C_signal;

end process;

-- synchronizer

process (clock_in)

begin

if (clock_in'event and clock_in = '1') then

V_out <= Vout_tmp;

end if;

end process;

(不等号は全角に換えてあります)

で、それを使ってこの間のビデオ出力のVHDLを

もう一回うごかしてみたんですが、なんとなく

チラチラと信号が安定しないのが気になってました。

TINY2313のクロック源がブレッドボードで安定してない

ことが原因かなぁと思っていたんですが、どうやら

そうではなさそうな気が…

修正後のVHDLを動かしてみたあと、A.C.さんが

「3ビットDAC」のお話をされていたのを受けて、

出力する抵抗の下位から1個、2個と取り外していって

3ビットDACまで減らしてみたんですが、そしたら

なんとなく映像がクリアになったんですよね。

ということは、原因はCPLD側にある様な気が…

VHDLの内容は後でもうちょっとブラッシュアップ

する必要がある気がするな…

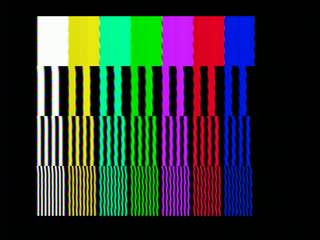

ちなみに3ビットDACにしてみた時の映像です。

例によって水色が緑っぽく見えますが、これは

ビデオキャプチャーのせいです。テレビには水色で

表示されます。5ビットDACとは若干発色が

ことなりますが、8色表示として変ではありません。

うーん、3ビットでも結構いけてるジャン!

4ビットについては5ビットとの違いが殆どわかり

ませんでした。もともと5ビットなんでいらなかった

ってことかな?

4ビットにするなら、フルアダーの回路規模ももう少し

小さく出来るだろうし、抵抗もカーボン皮膜で

充分じゃないかなぁ?

|