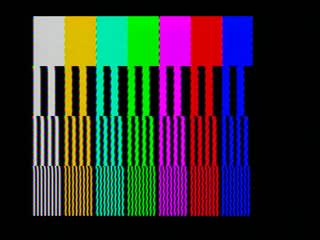

この間のCPLDで作ったコンポジットビデオ表示の

VHDL。入力するビデオ信号の水平同期期間が少し

ズレる場合、実験の結果から見ると横方向に周期的

な歪みが生じて、映像が横に揺れる感じになって

しまうっぽいとわかりました。

こんな風に、映像がフニャフニャうねうねします。

多分、14.3Mhzの1クロック分に相当するのでは?

水平同期期間が63.4usからズレていることによって、

CPLD側のクロックとTINY2313側のクロックそれぞれ

の微妙なズレがこのうねうねとしたウネリを作り

出しているものと予想してみました。

では、水平同期期間をもう少し正確にしたらどうなるか。

それを実験してみました。TINY2313に入れたプログラム

を少し修正し、水平同期期間を64.3us→63.4usにして

みます。

こんな風になりました。一見してうねうねが少なくなって

いるのが判るかと思います。

ゼロにはなってませんけどね…。

というわけで、とりあえず63.4usに近づけることで

うねうねは軽減することは出来そうだけど、

一方、1クロック単位でタイミングを合わせないと

うねうねは消せそうに無いということが見えてきました。

(もっと言うと、14.3Mhzの4クロック単位で

上手くシンクロすれば、うねうねは消える

はずなんですが…)

この構成であれば、CPLD用のクロック源を

マイコン側にも流用することによって

プログラム上でも正確に910クロックで1ライン

描くといった感じの処理にすれば綺麗に表示

できる様な気がします。

でもいちばん簡単なのはやっぱり、CPLD内部

で映像信号自体を作り出すことだな…

そうすれば、クロックがずれるということは

(理論上)起らないので。

VHDLは一応できちゃったから、これをもとに

してもう少し大きなCPLD…たとえばトラ技

2006年4月号付録とか使って、簡単なカラー

映像の表示処理でもやってみればハッキリする

んだけどな…。

|

|

|