彦根藩二代当主である井伊直孝公をお寺の門前で手招き雷雨から救ったと伝えら

れる"招き猫"と、井伊軍団のシンボルとも言える赤備え。戦国時代の軍団編成の

一種で、あらゆる武具を朱塗りにした部隊編のこと)の兜(かぶと)を合体させ

たせて生まれたキャラクタ。

【今日のSDGs食事:牛筋煮込み編】 完熟みそ牛すじ土手鍋

完熟みそ牛すじ土手鍋

突然、思いつく。そうだ「すじ肉を安く手に入れおいしい土手鍋をつくろう」と。

しかし、仕入れ方法から調査しなければないらい。牛肉だけではない、鳥、豚も

そうだ。時間をかけてみよう。そういえば、石井さん(故人)が初めて教えてく

れ、仕事帰りにおいしく頂いたあの頃をなつかしく回想する。

【災害用トイレ考 ①】

トイレの備えがあなたの命と健康を守る。土木建設の現地トイレを利用した肩な

らわかってもらるが、管理が悪い事業者なら野糞状態で荒れ果て不衛生的でこの

上ないが。台風をはじめとする風水害では、河川の氾濫や雨水の逆流などで、街

が浸水することもあり。地震や停電被害にあったマンションも、配管の破裂など

で電気設備が水没で配電盤が故障・停電、断水する。私達が普段なにげなく使っ

ている水洗トイレは、「給水」「電気」「排水設備」が正常に機能してはじめて

気持ちよく使えるシステム。

仮設トイレのイメージ

東日本大震災では、災害発生から3~6時間ほどで、半数以上の人がトイレに行き

たくなったと答えている。しかしながら、仮設トイレが設置されるまでには4日

以上かかったところが半数以上。また災害時は、極度のストレスにより体調を崩

し下痢やおう吐もあり。そんなときにトイレが使えない状態だとよりストレスが

かかり悪化。「トイレに行かない」「我慢する」「トイレに行く回数を少なくす

る」ために水分や食事を控えてしまうと、脱水による体力低下(免疫力の低下)、

尿路感染症(膀胱炎等)、循環不全(肺塞栓等)のなどを引き起こす危険性が非

常に高くなる。脱水傾向となり血液粘度が上昇すれば、エコノミークラス症候群

を発症するリスクも高くなる。

エコノミークラス症候群を発症するリスク

中越地震を例に挙げると、発生から14日までの調査では車中泊者に14件の肺塞栓

症での入院が確認され、そのうち7人つまり半数の死亡が確認された。東日本大

震災では、「エコノミークラス症候群」医療チームが避難所を巡回し、エコー検

査を1,000人超の被災者に対しスクリーニングしたところ、約10%に血栓ができて

いた(エコノミークラス症候群を発症する可能性があった)。また、熊本地震で

は死者263人のうち、エコノミークラス症候群を含む「震災関連死」はその5分の

4にあたる208人にのぼり、入院を必要とした「エコノミークラス症候群」患者数

は50人にも上った。

解決方法は?

災害によってトイレが使えなくなることや、トイレが使えないことによって、精

神的にも身体的にも大きな問題が出てくることがお分かりいただけたことと思う。

それではこの問題を解決は? あります!それこそが「携帯トイレ」や「簡易トイ

レ」。トイレの備えが、災害時のあなたの命と健康を守ってくれる!

------------------------------------------------------------------------

•簡易トイレと携帯トイレがある

•簡易トイレは便座あり

•携帯トイレは便座なし

•使う環境を想定し、品質の確かな製品を選ぶ

------------------------------------------------------------------------

可動型簡易トイレ

大便用携帯トイレ

⛑ まだまだ改良の余地が残っている(➲革命的設計変更)。

黒の革命

黒の革命

世界初|グラフェンから作られた機能性半導体

1月9日、グラフェンから作られた最初の機能性半導体がジョージア工科大学で作

製されました。これにより、電子デバイスの小型化と高速化が可能になり、量子

コンピューティングへの応用が期待されている。半導体は、特定の条件下で電気

を伝導する材料であり、コンピューター、ラップトップ、スマートフォンのチッ

プなどの電子機器の基礎コンポーネント。 何十年にもわたり、そのアーキテク

チャはますます小型化し、よりコンパクトになってきた。これはムーアの法則と

して知られる特長。一般的なコンピューティング速度やビデオ・ゲームのグラフ

ィックスから、医療スキャンの解像度や天文台の感度に至るまで、広範なテクノ

ロジーの大きな飛躍する。マイクロエレクトロニクスの主な素材であるシリコン

は、小型化の点で物理的限界に近づきある。 たとえば、台湾積体電子製造会社

(TSMC)は、2028年までに1.4ナノメートル(nm)プロセスのノードをリリー

スすると予想されている。コンピューティングの高速化と小型化の進歩には、新

しい材料とチップ構造が必要。2004年に発見されたグラフェンは、単層の炭素か

ら作られるナノテクノロジーの一種。半導体分野における潜在的な変革をもたら

すことが喧伝され、その注目すべき並外れた導電性、柔軟性、強度が含まれる。

同研究者らは、原子1個の厚さの極薄構造を利用し、さらに小さく、より効率的

で、高速なチップ開発方法を模索。同研究者らは、グラフェンから作られた世界

初の完全に機能する半導体を実証し、この分野における重要なマイルストーンを

達成した。現在、シリコンの10倍の移動度を持ち、シリコンでは得られない独特

の特性を備えた非常に堅牢なグラフェン半導体を入手。言い換えれば、電子は非

常に低抵抗で移動し、より高速なコンピューティングにつながる。例えれば砂利

道を運転するのと高速道路を運転するようなもの(ウォルター・デ・ヒーア大学

教授)。コンピュータチップの標準材料であるシリコンでは、電子移動度は通常、

室温で約 500cm²V⁻¹s⁻¹ ➲ デ・ヒール教授のチームは、5,000 cm²V⁻¹s⁻¹の移

動度を達成。この画期的な成果は、10年前の特殊炉を使用し、炭化ケイ素ウェー

ハ上にグラフェン成長法を発見した研究の集大成であり、炭化ケイ素の結晶面上

に成長させたエピタキシャルグラフェン単層を生成。適切に製造すると、エピタ

キシャルグラフェンが炭化ケイ素に化学結合し、半導体特性を示し始めることを

発見。同社の製品は現在、ナノエレクトロニクスで必要な特性をすべて備えてい

る唯一の二次元半導体であり、その電気特性はトップデータ。

グラフェンエレクトロニクスにおける長年の問題は、グラフェンが適切なバンド

ギャップを持たず、正しい比率でオンとオフを切り替えることができないことに

あった。この技術はバンドギャップを達成し、グラフェンベースのエレクトロニ

クスを実現めの重要なステップとなる。

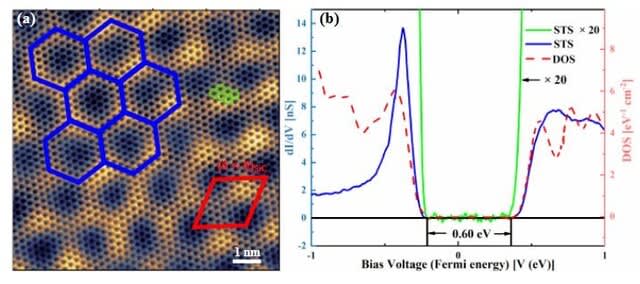

グラフェンハニカム格子の原子分解能画像

クレジット: De Heer et.al (Nature,2024)

この材料により、たとえば、量子コンピューティングの要件である電子の量子力

学的波動特性がを利用できる。しかし、シリコンはエレクトロニクスの歴史にお

けるいくつかのステップの最新のものにすぎず、ある時点で新世代のエレクトロ

ニクスに代替される。将来的には別のパラダイムシフトが避けられず、グラフェ

ン置き換わるだろう。

【掲載論文】

・原 題:炭化ケイ素上への超高移動度半導体エピタキシャルグラフェン

Ultrahigh-mobility semiconducting epitaxial graphene on silicon carbide

PMD 38172363 DOI: 10.1038/s41586-023-06811-0

【要約】

エピグラフェンは、単結晶の炭化ケイ素(SiC)基板上にエピタキシャル成長した

グラフェン、ミレニアムの初めにムーアのロードマップをシリコンを超えてるた

めの道筋が提案されたが、グラフェンと基板上の段差バンドギャップがないこと

が障害となり続けた。本研究では、SiC表面に結合したグラフェンのような界面で

覆われたミリメートルスケールの段差のないテラス作製方法を紹介する。このバ

ッファ層は、0.6eVのバンドギャップと4000 cm²V⁻¹s⁻¹を超える室温移動度を持

つ2次元半導体エピグラフェン(SEG)、現在のすべての2次元単層半導体を10倍

も上回る。トップゲートSEG電界効果トランジスタは、デジタルエレクトロニク

スに適した10⁴のオン/オフ比を示す。さらに、水素インターカレーションにより

SEGがSEGとシームレスに統合できる高移動度の半金属エピグラフェン単分子膜

に変換することも判明。この準自立単分子膜のエピグラフェンエッジ状態では、

センチメートルスケールの平均自由行程が観察され、これは1000倍であり、あら

ゆる材料で観測された最大の室温電子平均自由行程となる。

図1.(a)CCS法(左)では、3.5mm×4.5mmのSiCチップを、リーク付きの閉じた円

筒形のグラファイトるつぼに入れる。るつぼは真空またはAr雰囲気で加熱され、

Siが蒸発し、最終的に漏れから脱出。炭素に富むSiC表面が結晶化してバッファ

層を形成。SE-CCS法(右)では、下チップのC面と上チップのSi面を向くように2チ

ップを積層する。底面チップのSi面はポリマーでコーティングされており、底面

チップを炭化して坩堝壁に効果的にはんだ付けするために、チップが高温で導通

したときに渦電流が通過します。2つのチップ間のわずかな温度差により、下部

チップから上部チップへの正味の質量流量が発生し、上部チップ上に大きなテラ

スが成長する。シリコンがゆっくりとエスケープすると、SEG層が形成される。

(b)真空中で昇華して緩衝層を生成の算出成長時間(青)。真空中でのCCS法(緑)。

10 mBar Ar(黒の破線)のCCS法。1Bar Ar(黒)のCCS法。また、SE-CCS法で高さ100

nm、幅100nm/tan(Q)の段丘を持つステップを生成に必要な時間も示す(Qは、基板

のミスカット角度)。(c)SEGは3段階で成長する。ステージ(I)では、真空中でチ

ップを900℃に加熱し、表面をきれいにし、ポリマーを炭化させます。ステージ

(Ⅱ)は、1300℃、1バールArで、2層SiCステップの規則的なアレイと≈0.2μm幅

のテラスを生成。ステージ(Ⅲ)は、1600℃、1バールArで、SEGでコーティングさ

れた最大1mm幅の原子レベルで平坦なマクロテラスを生成する。

図2.アルミナトップゲート450 μm x 80 μm QFSGリボンの輸送測定。

(a) 電子と正孔の電界効果移動度は、(b)の破線に対応する最大傾きdG(Vg)/dVg

から求める。裸のQFSGと比較して移動度が100倍に低下したのは、図5(g)はアル

ミナによる。(b)のG(Vg)の形状は短距離散乱と一致する。p-ドーピングは、温度

の上昇とともにわずかに減少する。ただし、最も顕著な効果は、非常に大きなコ

ンダクタンスプラトーで、示されるようにdG(Vg)/dVgタンジェントの交点により

定量化され、挿入図の温度によりソートされる。1 G0 プラトーは、コンダクタ

ンスの半分以上がエッジ状態からのものであることを示す。その(室温)平均自由

行程は1cmを超え、これは2Dグラフェン状態の平均自由行程(mfp)よりも5x10 6倍

大きく、このリボンのエッジの450μmの長さに沿った無秩序と温度に対して非常

に鈍感であることを示す。

【概要】

図 1 SEG の製造 (a) CCS 法 (左) では、3.5 mm x 4.5 mm の SiC チップが、

リークが供給された密閉円筒状グラファイトるつぼに配置。るつぼは真空または

Ar 雰囲気中で加熱され、Si が蒸発し、最終的にはリークから流出。炭素が豊富

な SiC 表面は結晶化してバッファ層を生成。

SE-CCS 法 (右) では、2つのチップが、下部チップの C 面が上部チップの Si

面に面するように積層。底部チップの Si 面はポリマーでコーティングされ、炭

化し底部チップをるつぼ壁に効果的にはんだ付けに、チップが高温で導通状態に

なったときに渦電流が通過でききる。2つのチップ間のわずかな温度差により、

底部のチップから上部のチップへの正味質量流が生じ、その結果、上部のチップ

に大きなテラスが成長する。

シリコンがゆっくりと逃げることで、SEG 層が形成される。 (b) 真空中での昇

華によってバッファ層を生成するための計算された成長時間 (青)。真空でのCCS

法 (緑色)。 10 mBarArでのCCSメソッド (黒の破線)。1BarAr(黒)のCCS方式。

また、SE-CCS 法で、幅 100 nm/tan(Q) のテラスを備えた高さ 100 nm のステッ

プを生成するのに必要な時間も示す。ここで、Qは基板のミスカット角度。 (c)

SEGは3段階で成長。 段階 (I) では、真空中でチップが 900℃ に加熱され、表

面が洗浄され、ポリマーが炭化される。1バールAr中、1300℃での段階

(Ⅱ)は、二層SiCステップの規則的な配列と約0.2μm幅のテラスを生成

する。1 Bar Ar中で1600℃のステージ(Ⅲ)では、SEGでコーティングされた最大

1mm幅の原子的に平坦なマクロテラス生成される。

図2.SEG コーティングされた SiC マクロテラスの特性

(a) 幅 300 μmのテラスを SEM で画像化し、濃い灰色のバッファ層と明るい灰

色の SiC表面の間に大きなコントラストが生じるように焦点を合わせる。テラス

は高さ 100nmの左ステップ (顕微鏡写真の赤線) から右ステップ (顕微鏡写真の

緑線) まで伸びています。AからBまでのラインをその全長に沿って AFMでプロー

ブし、5μm×4μm の領域 a、b、c を3回スキャンすることで、テラスが原子的

に平坦であることが確認されます。挿入図は、SiC 表面に共有結合したバッファ

層の概略断面図を示す。(b) 50μm x 50μm の領域にわたるラマン・マップの例

(2500 個の個別スペクトル)。各スペクトルはバッファ層と一致する。 A とマー

クされた赤い矢印は、高い I2D/IG 比 (0.109) を持つ赤いスキャンが行われた

場所を示しているが、スキャンでは分解された 2Dピークが示されていない。Bと

マークされた青色の矢印は、I2D/IG 比が低い (0.01) 青色のスキャンが取得さ

れた場所を示す。どちらの場合も、表面には検出可能なグラフェンはない。

図3.SEGの特性評価

(a) バッファ層の低温原子分解能 STM 画像は、下にある SiC基板の規則的な (6

x6) SiC 超周期構造 (赤い菱形、紫色の六角形) によって空間的に変調されたグ

ラフェン ハニカム格子 (緑色) を示す。 高さの変調は、エピタキシャルバッフ

ァ層と基板の共有結合によるもの。 (b) バッファ層 (青) の STS は、0.6 eV

の明確なエネルギーギャップを示す。 垂直 20倍ズーム (緑色の線) では、ギャ

ップ内の状態の証拠は示されていない。 赤い破線は計算された状態密度。(過小

評価された計算ギャップは、STSスペクトルに適合するように 50%拡大する)。

計算された特徴は観測結果とよく一致する。

図4.QFSG の特性評価

(a) 水素インターカレーションによって生成された QFSG の 20 μm × 20 μm

領域の低温 STM は、欠陥がないことを示す。 (b) 25 μm x 25 μm 領域のラマ

ン マップは、裸の SiC やバッファーがなく、グラフェンで完全に覆われている

ことを示す。 A とラベル付けされた矢印は、I2D/IG=3.73 (赤スキャン) の領域

を指し、B とラベル付けされた矢印は、I2D/IG=1.75 (赤スキャン) の領域を指

す。グラフェンではこのサイズのばらつきが普通である。

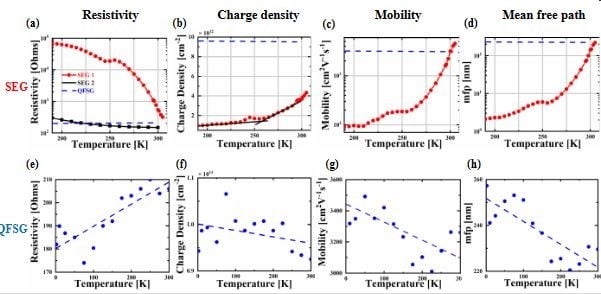

図5.裸の SEG (a ~ d) と裸の QFSG (e ~ h) を比較したトランスポートと

ホールの測定。 (a) SEG1 の抵抗率は 190 K での 70 kW から 305 K での 319W

に減少するが、SEG2 では 180 K での 300 W から 300 K で 130 W に減少。

サンプル間の差は電荷の違いを反映。加工による濃さ。 (b) SEG1 の電荷密度は、

190 K での 1.0 x 1012 cm-2 から 300 K での 3.7 x 1012 cm-2 に増加。(c)は、1

90 K での 93 から 305 K での 4525 cm2V-1s-1 への移動度の増加を示す。

これは、低温ではバンド端付近でトラッピングが発生することを示す。 SEG1の

平均自由行程は190Kで2.1nmであり、これは(6x6)SiC超周期格子の格子定数(図

3a)に近いため、関連するトラップメカニズムを示唆しています(本文を参照)。

平均自由行程は 305 Kで 219 nmに増加し、QFSG の平均自由行程に近づく (青い

破線)。 (e-h) から明らかなように、QFSG の特性は、フォノン散乱が弱いため、

グラフェン一般の場合と同様に、基本的に 1.8 K から 300 K までの温度の影響

を受けません。これも SEGを他の 2D半導体とは区別する。

図6.アルミナトップゲートの 450 µm x 80 µm QFSG リボンの輸送測定

(a) 電子および正孔の電界効果移動度は、(b) の破線に対応する最大傾き dG(Vg)

/dVg から決定されます。 裸の QFSG と比較して移動度が100分の1に減少 (図5(

g)) のは、アルミナによるもの。 (b) の G(Vg) の形状は短距離散乱と一致。

p型ドーピングは、温度が上昇してもわずかに減少するだけである。ただし、最

も顕著な効果は非常に大きなコンダクタンス・プラトーであり、示されているよ

うに dG(Vg)/dVg 接線の交差点によって定量化され、挿入図では温度により分類

されている。 1 G0 プラトーは、コンダクタンスの半分以上がエッジ状態からの

ものであることを示す。 その(室温)平均自由行程は 1 cmより大きくなり。こ

れは 2D グラフェン状態の平均自由行程(mfp)よりも 5x106倍大きく、これはリ

ボン端の450μmの長さに沿った温度の乱れに対し極めて鈍感であることを示す。

【関係技術情報】

・エピタキシャルグラフェンの構造と物性

特集 電子線で何が観測できるか 名古屋大学大学院工学研究科 乗松 航

日本結晶学会誌 61,35-42(2019)

この項了

この項了

● 今夜の寸評:日本海

冬の演歌と言えば、ジェロが唄う『海雪』

※コメント投稿者のブログIDはブログ作成者のみに通知されます